目录

- 前言

- 1 D-PHY 简述

- 2 D-PHY硬件结构

- 3 D-PHY Operation

- 4 Fault Detection

- 5 Global Operation Flow Diagram

前言

前言出处:CSDN 爱洋葱

MIPI 接口广泛用于摄像头和显示器件;PHY 属于 MIPI 接口的最底层部分,也就是物理层,直接涉及到物理连线,信号传输等等。

MIPI 多媒体部分的 PHY主要分为了 3 种:

- D-PHY

- C-PHY

- M-PHY

可以在 MIPI 的官方网站上去搜索这些 PHY 的 Specification;需要额外说一下的是,D-PHY 最先出来,现在用得很多,传输速度快;M-PHY 再出来,速度最快,但是与 D-PHY 不兼容,而且受限于其他器件的发展,如此高的带宽,暂时用不上;最后出来的是 C-PHY,没有时钟信号,靠 pin 脚的编码来区分数据信号。

Note:C-PHY 和 D-PHY 的 C 和 D,不是 Camera 和 display 的简写,只是 PHY 的命名;D-PHY

可以接 CSI 成为摄像头端的 PHY,也可以用在 DSI,作为 display 的 PHY;C-PHY 也一样。

本篇介绍的是 D-PHY,在 MIPI 的官网上可以看到 D-PHY 其实也分了很多的版本,也就是说,现在 MIPI 联盟中,发展了几个 PHY 的标准,而这几个 PHY 的标准又各自有不同的版本。具体如下:

多说两句,D-PHY 中的这个 D,在罗马数字中代表了 “500”,那么 D-PHY 含义就是 500-PHY,也就是这个这个 PHY 最初设计是跑 500MHz,由于是 DDR 的时钟,所以理论上就是 1Gbps/per Lane 的速率;

1 D-PHY 简述

D-PHY 描述了一种源同步、高速、低功耗、低成本的 PHY。D-PHY 规范主要用于将相机和显示应用程序连接到主机处理器。和大部分总线一样也分Master-Slave端,且由于链路两侧之间的主从关系,链路的操作和可用数据速率是不对称的。这种不对称设计也降低了链路的复杂性。同时双向、半双工操作等一些特性是可选的,具有很大的灵活性。

D-PHY 在 Master 和 Slave 之间提供同步连接。一个基本的 PHY 配置由一个时钟信号(Clock Lane) + 一个或多个数据信号(Data Lane)组成。

- Clock Lane是单向的,由Master端发向Slave端。

- Data Lane 可以是单向或双向

对于半双工操作,反向带宽是正向带宽的四分之一。

D-PHY包含两种模式:

- High-Speed Mode——主要用于高速数据传输

- Low-Power Mode——主要用于控制,但还有其他可选用例。

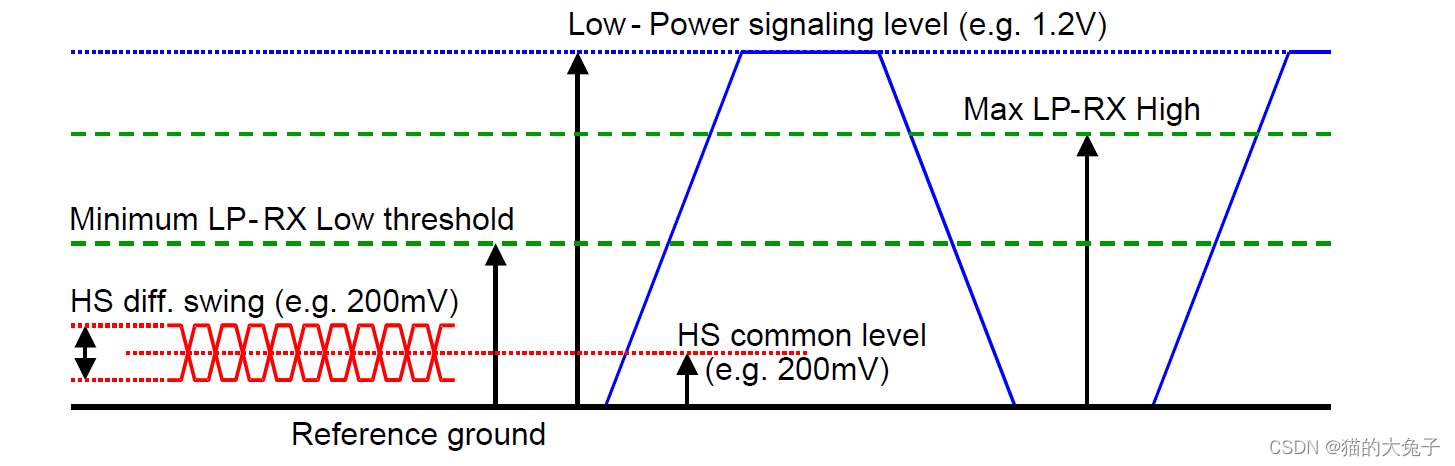

在高速模式下,每条通道都在两侧端接,并由低摆幅、差分信号驱动,一般为200 mV。高速单条Data Lane的速率上限一般为2.5Gbps。

在低功耗模式下,所有电线均以单端和非端接方式运行。出于 EMI 的原因,该模式的驱动器应受压摆率控制和电流限制,其电压一般为1.2V。低功耗模式下的最大数据速率为 10 Mbps。

2 D-PHY硬件结构

2.1 Lane模型

一个 D-PHY 包含一个时钟通道模块和一个或多个数据通道模块。这些 D-PHY 通道模块中的每一个都通过两条线路与通道互连另一侧的互补部分进行通信。一个通用的 D-PHY 包含了 LP-TX、LP-RX、HS-TX、HS-RX、LP-CD,最后对外的接口是 Dp 和 Dn(差分信号)。

其中HS-TX、HS-RX 即为High-Speed模式,该模式下Dp和Dn为差分信号,使能端接。

其中LP-TX、LP-RX、LP-CD 即为Low-Power 模式,该模式下Dp和Dn则非差分信号,也关闭端接。

D-PHY至少由一条Clock Lane和一条Data Lane组成。

值得一说的是,Master需要一个 PLL 时钟乘法器来生成高频时钟。D-PHY 规范使用架构模型,其中 PHY 外部的单独时钟乘法器单元为 PHY 生成所需的高频时钟信号,该时钟由开发者决定。

则硬件框图如下所示:

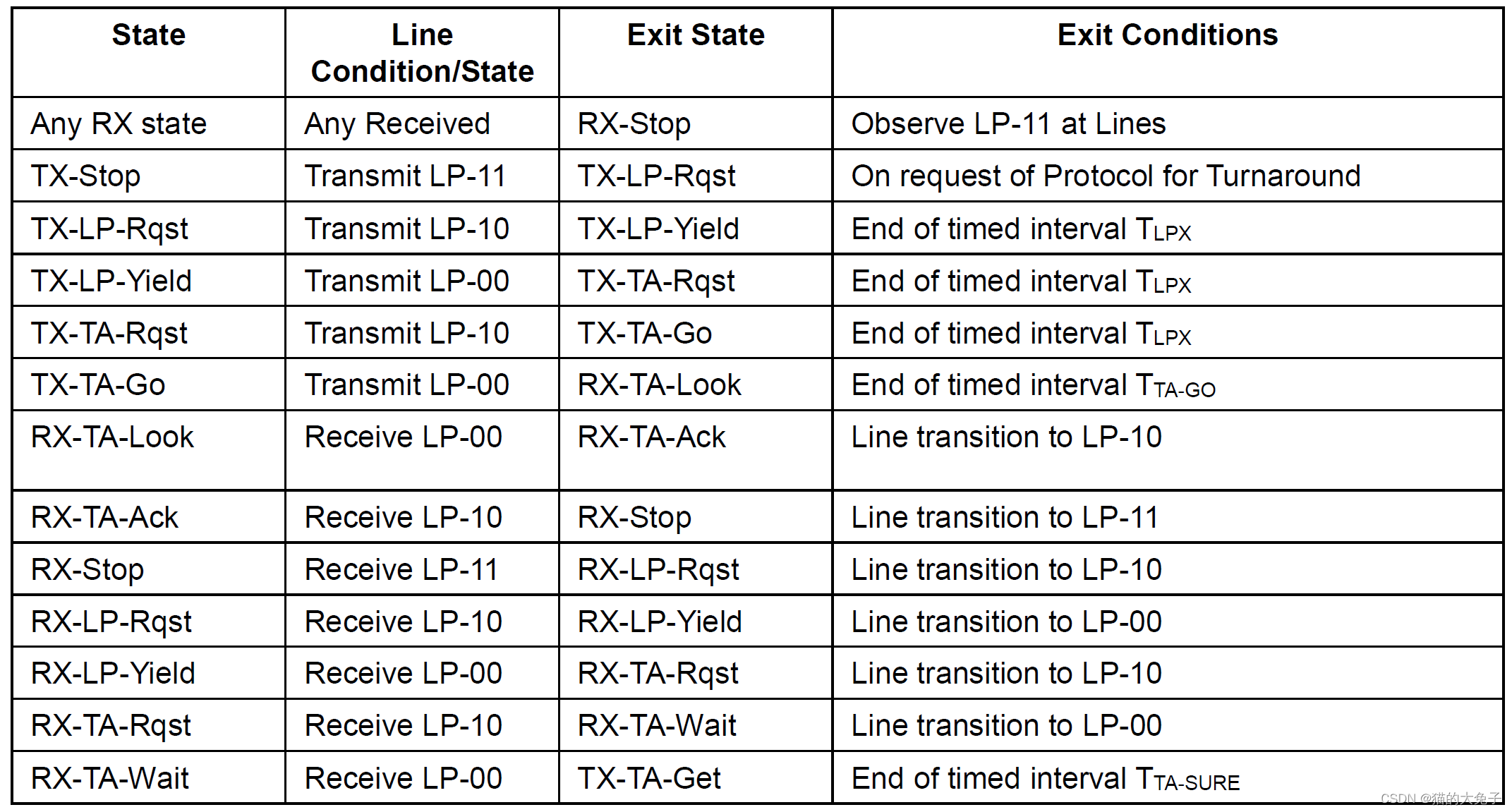

2.2 D-PHY Lane State

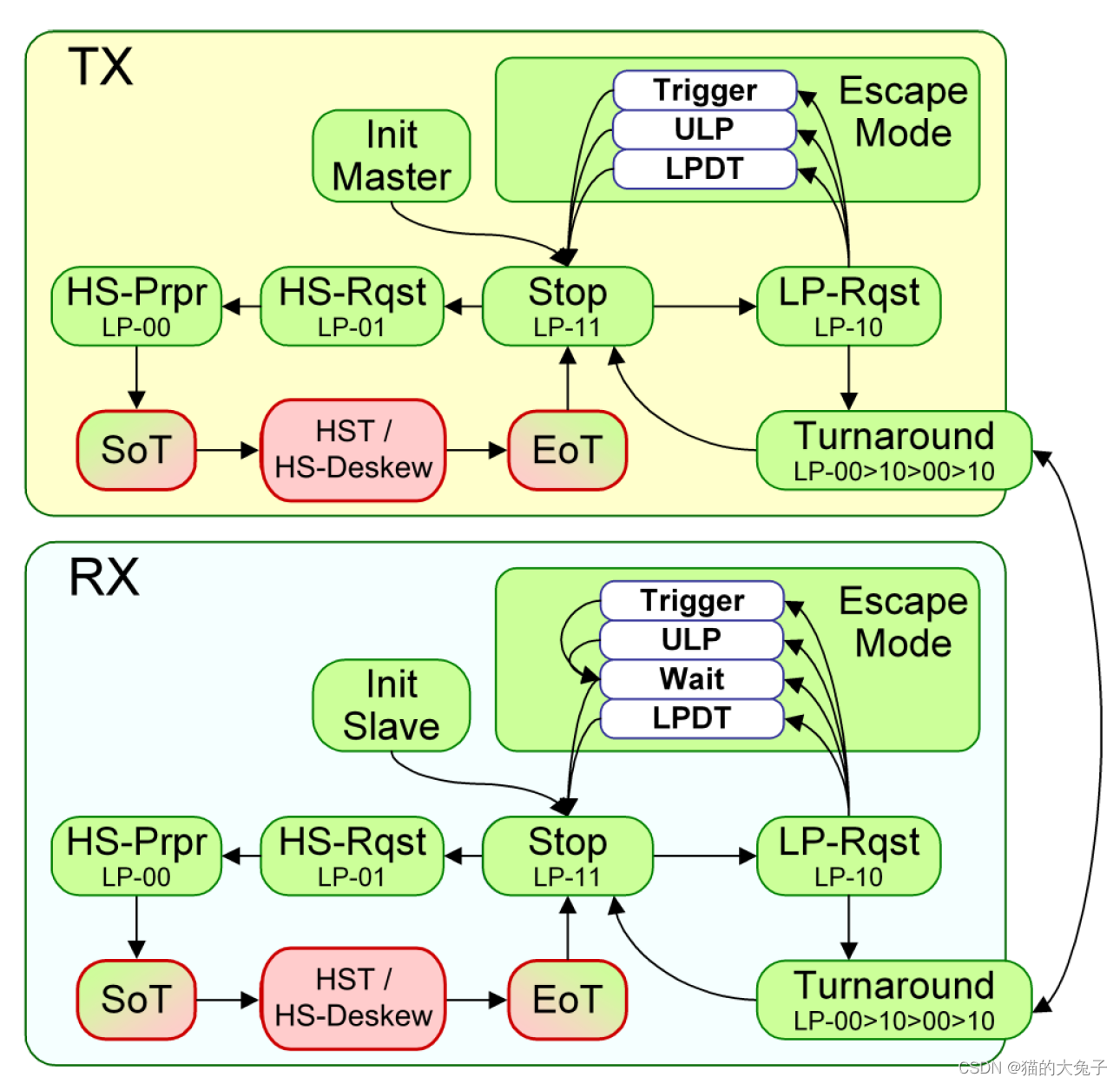

Data Lane多种模式下,具有不同的行为,那这些行为是如何定义的,即如何进入HS模式,如何进入LP模式,又如何进入Escape Mode下的多种模式。这些都是通过Spec规定好的状态来决定的。如下图:

Note: HS:是 High-Speed 的简写 LP:是 Low-Power 的简写

MIPI 在 D-PHY 层定义了一些状态(High-Speed、Control Mode、Escape Mode),那么我们要怎么和对端协商,或者换句话来说,我们要怎么进入对应的模式,并且告知对端呢?通常的情况下,一些通信协议可能会将状态码以 Packets 的形式发送到对端,然后改变模式之类的,但是在 MIPI 的 D-PHY 中定义状态转换,就是靠这些 State Code;

接下来我们看看这些 State Code 是什么含义:

在High-Speed 模式下,Lane 的 2 根线是独立的,不代表差分信号,那么 2 根线就有 4 种表达方式:

HS-0:表示 High-Speed 模式下, Dp 那根线的数据是 0,由于 High-Speed 是差分信号,那么 Dn 固然就是 1;

HS-1:表示High-Speed 模式下, Dp 那根线的数据是 1,由于 High-Speed 是差分信号,那么 Dn 固然就是 0;

在 Low-Power 模式下,Lane 的 2 根线是独立的,不代表差分信号,那么 2 根线就有 4 种表达方式:

LP-00:表示在 Low-Power 模式下,Dp 那根线的数据是 0,Dn 那根线的数据是 0,

LP-01:表示在 Low-Power 模式下,Dp 那根线的数据是 0,Dn 那根线的数据是 1,

LP-10:表示在 Low-Power 模式下,Dp 那根线的数据是 1,Dn 那根线的数据是 0,

LP-11:表示在 Low-Power 模式下,Dp 那根线的数据是 1,Dn 那根线的数据是 1,

2.3 配置选项

正如前面所说,Lane的配置据有很大的灵活性。一般而言主要是选择如下(摘自Specification for D-PHY Version 1.2)

• Single or Multiple Data Lanes

• Bi-directional and/or Unidirectional Data Lane (per Lane)

• Supported types of Reverse communication (per Lane)

• Functionality supported by Escape mode (for each direction per Lane)

• Data transmission can be with 8-bit raw data (default) or using 8b9b encoded symbol

3 D-PHY Operation

在D-PHY的Spec中,定义了Data Lane和Clock Lane,同时也定义了两种模式:

- High-Speed Mode

- Low-Power Mode

即Data Lane与Clock Lane均有这两种模式,但是二者又有所不同。下面分别进行分析。

3.1 D-PHY Lane Operation

一般而言,Data Lane0同时具有High-Speed Mode 与 Low-Power Mode,而Data Lane1-Lane3仅用于High-Speed Mode进行使用。即Data Lane0为半双工双向传输Lane(当然这也是可裁剪的)。下面描述了D-PHY Data Lane的所有工作模式。在Low-Powe模式下分为Control Mode与Escape Mode,而Escape Mode进而又分成多个模式。接下来一个一个看。

图片来源:CSDN 爱洋葱

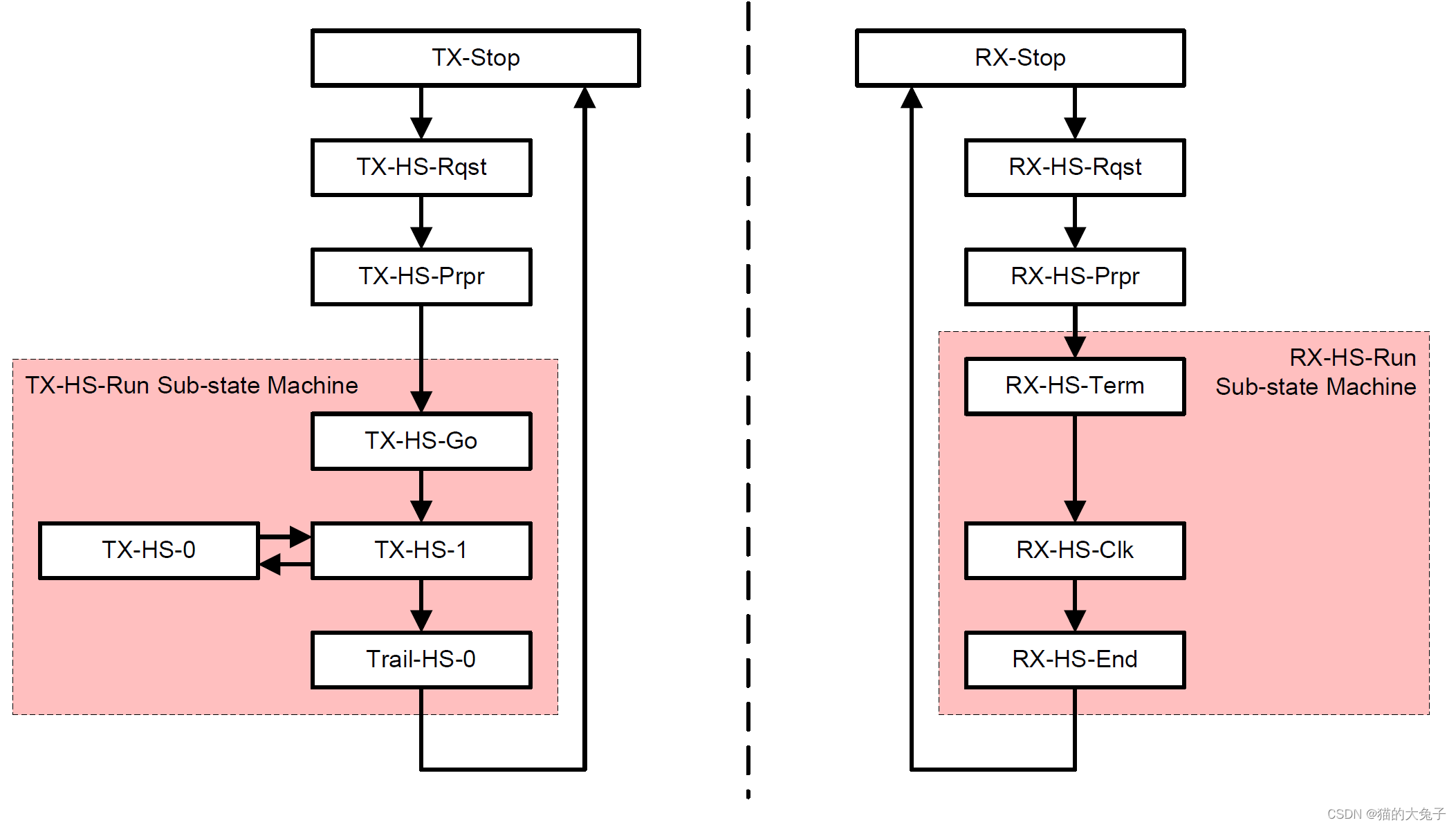

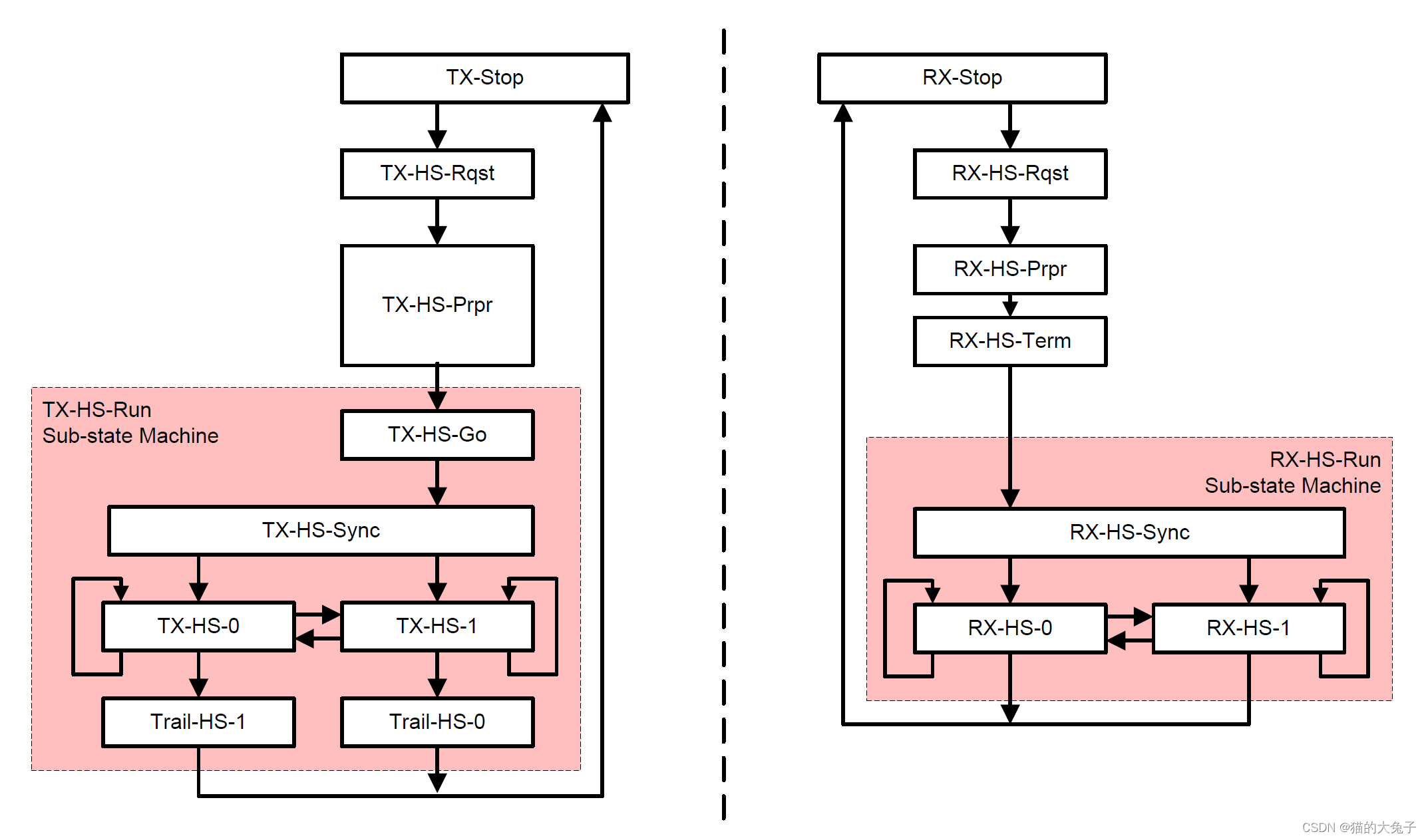

3.2 D-PHY Data Lane High-Speed Mode

高速数据传输以Burst发生。传输从停止状态开始并以停止状态结束。在Burst之间的中间时间期间,Data Lane应保持在Stop状态,除非在Lane上出现转向或退出请求。 在HS模式传输数据过程,Clock Lane处于高速模式,为从Slave端提供 DDR 时钟。

在D-PHY上传输的最小单位是Byte。

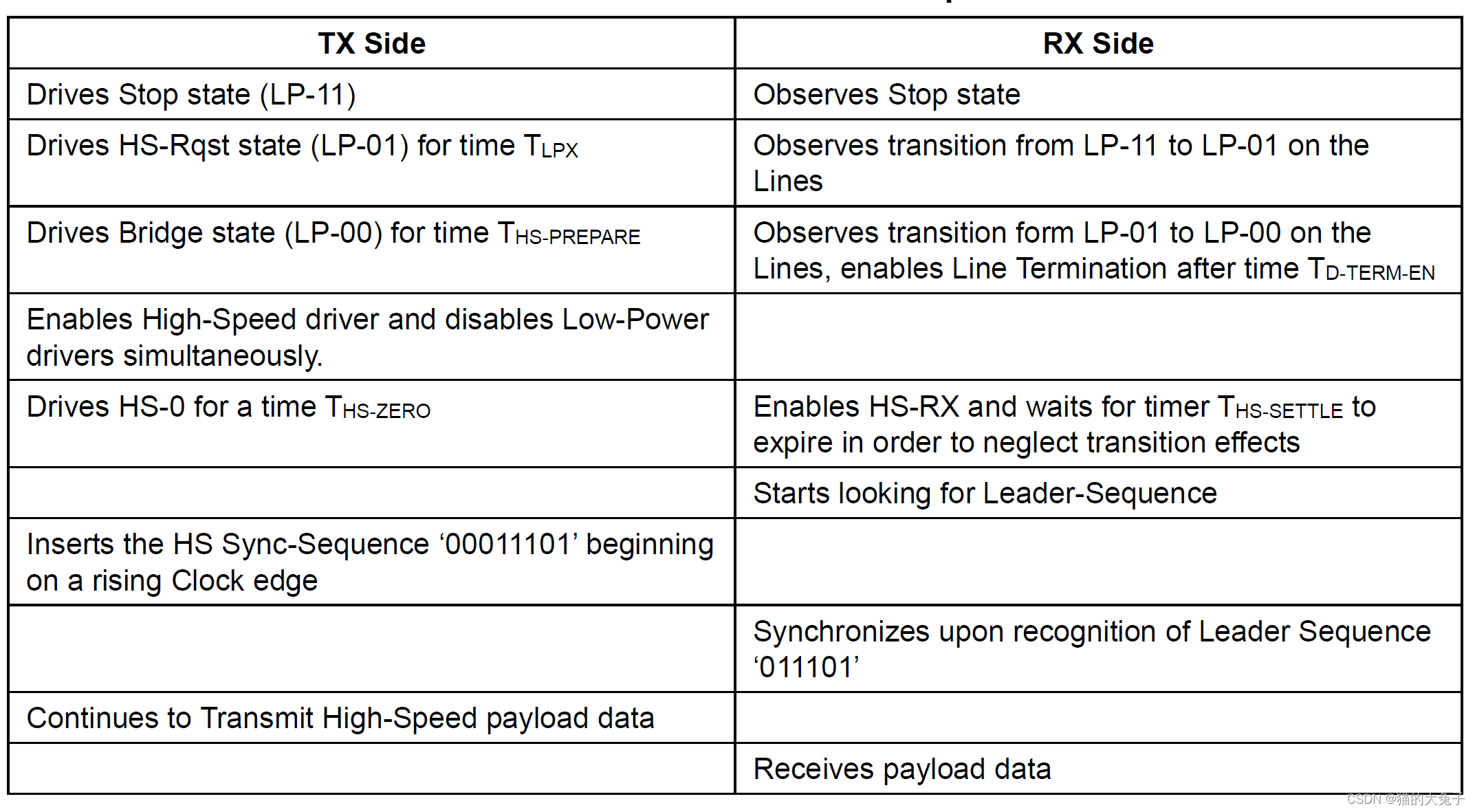

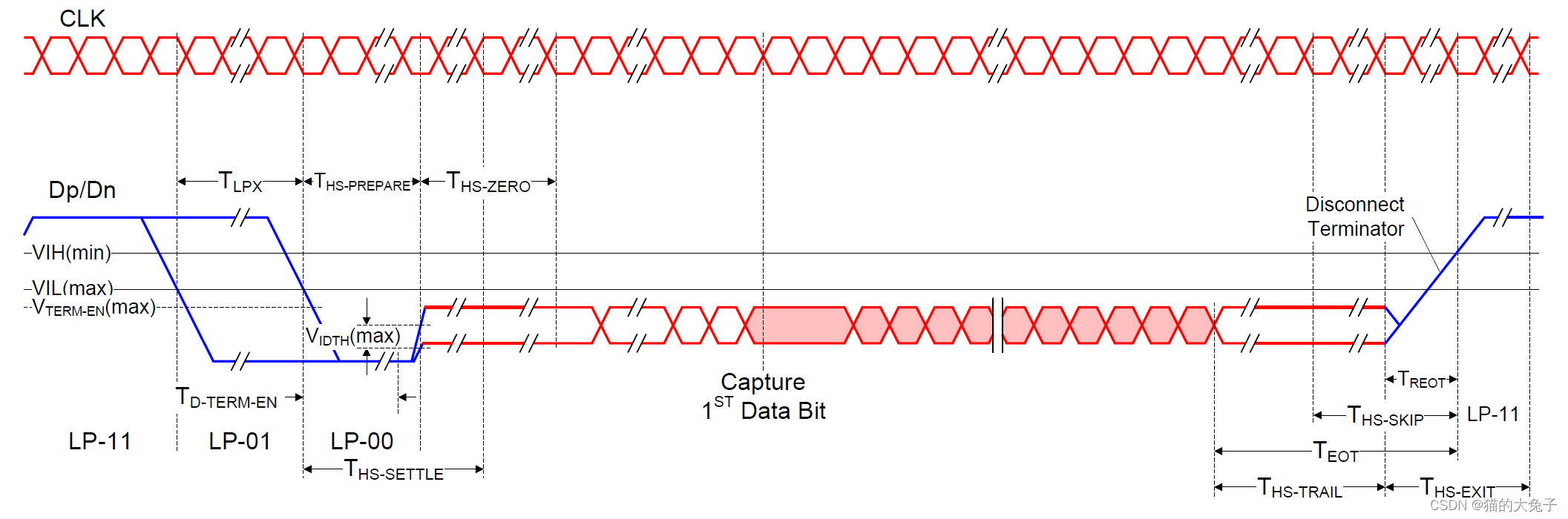

3.2.1 Start-of-Transmission

默认情况下,D-PHY处于IDLE状态,即LP11。那我们如何从这个状态切换到HS 模式并进行数据发送,并且对端也能知晓?答案就是通过发送我们约定好的序列。进入传输的序列即称之为Start-of-Transmission(SOT),同理也会存在其他推出的序列,进入其他模式的序列,后续意义分析。

SOT序列:LP11->LP01->LP00->HS0->HS Sync 序列(00011101)->send data

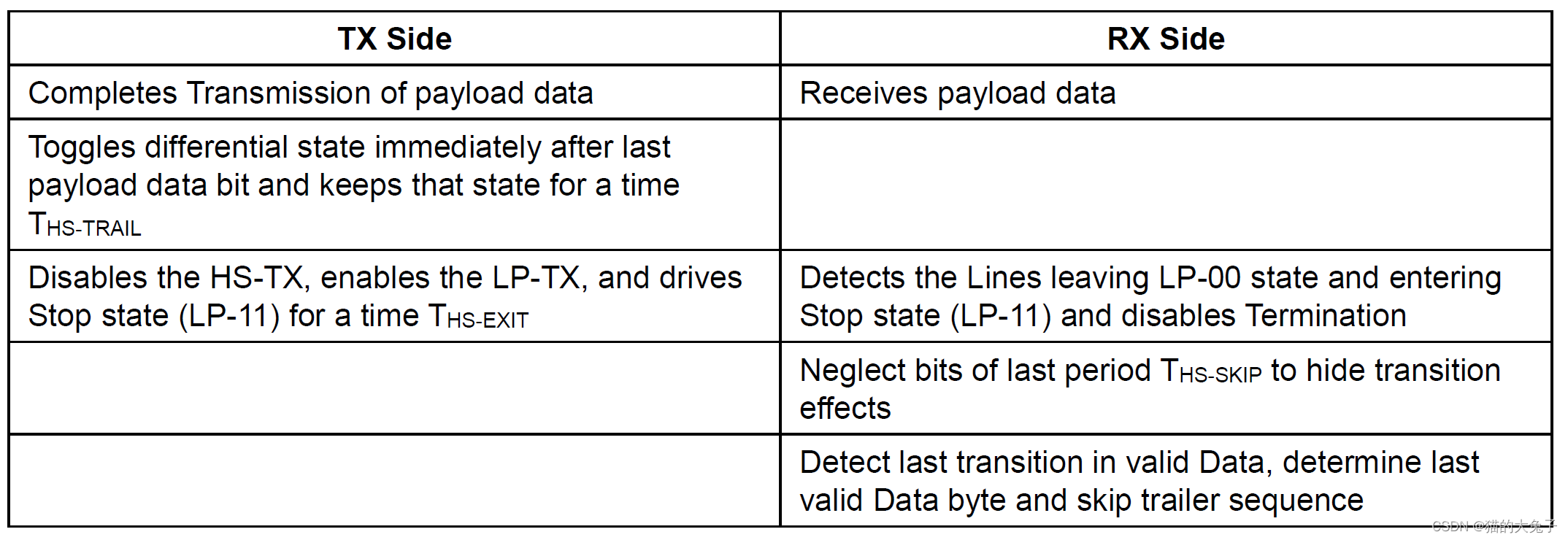

3.2.2 End-of-Transmission

既然后SOT,那么也应该存在EOT来切换自己状态到IDLE(Stop 状态)并同步对端。

EOT序列:LP11

3.2.3 HS Data Transmission

从3.2.1与3.2.2我们能知道如何开始与结束High-Speed的传输。从整个传输来看,即如下图,首先从Stop状态发送SOT进入High-Speed Mode,然后再以Burst方式进行数据传输,待数据传输完成之后,再发送EOT回到Stop状态。

3.3 D-PHY Data Lane Low-Power Mode

Data Lane的Low-Power模式分为Control Mode与Escape Mode,而Escape Mode又分为以下三类:

- Low-Power Data Transmission

- Ultra-Low Power State

- Reset-Trigger

3.3.1 Control Mode

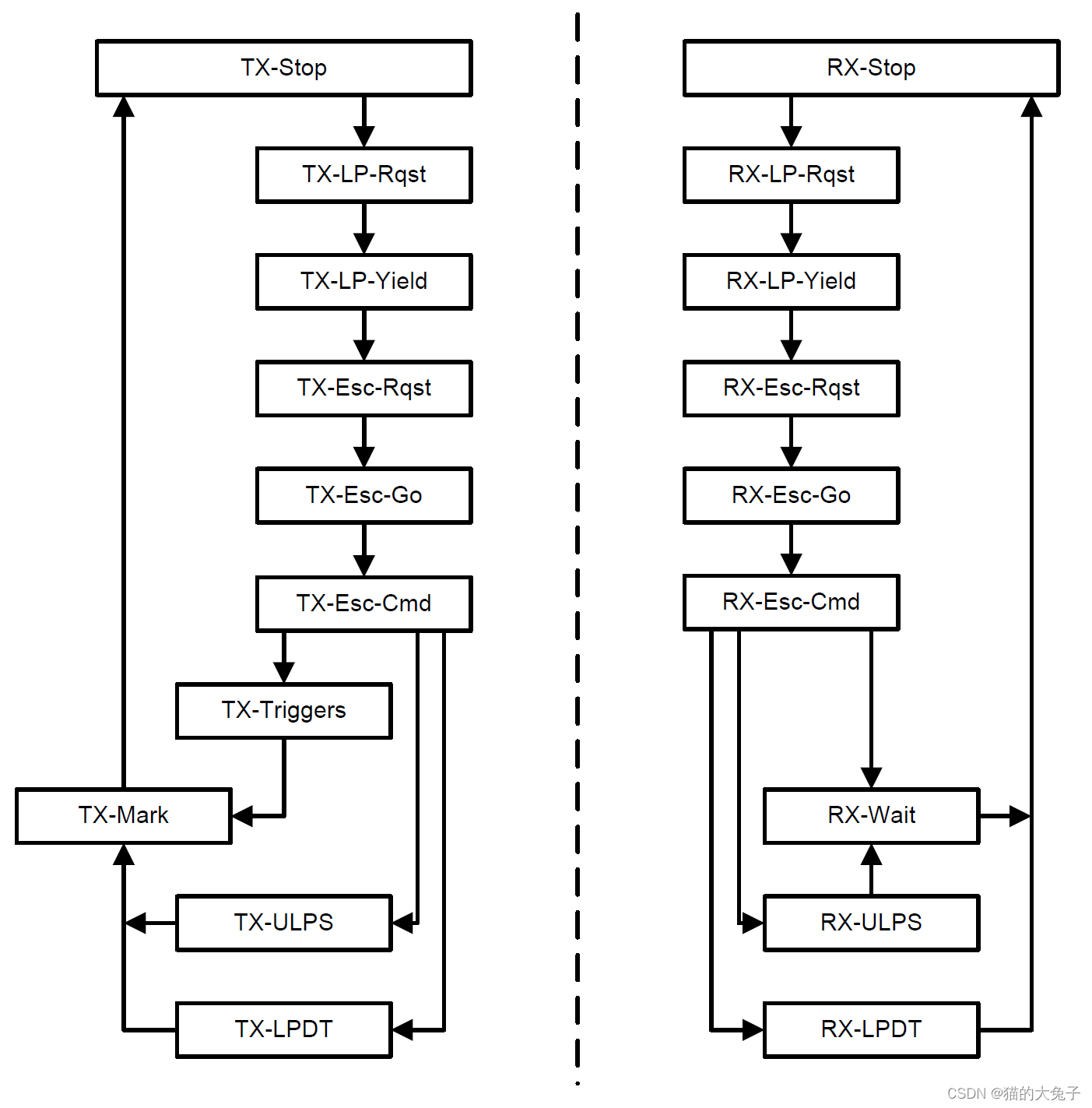

Control Mode是一个有趣的模式,它并不进行数据的传输,而是作为状态的管理,在我看来更像是一个桥。我们需要切换到High-Speed或者Escape Mode则需要先从Control Mode开始,并不能直接从High-Speed切换到Esccape Mode,就算半双工的BTA动作也是如此,在每次完成High-Speed传输或者Escape Mode的行为后,总是通过LP11返回Control Mode。

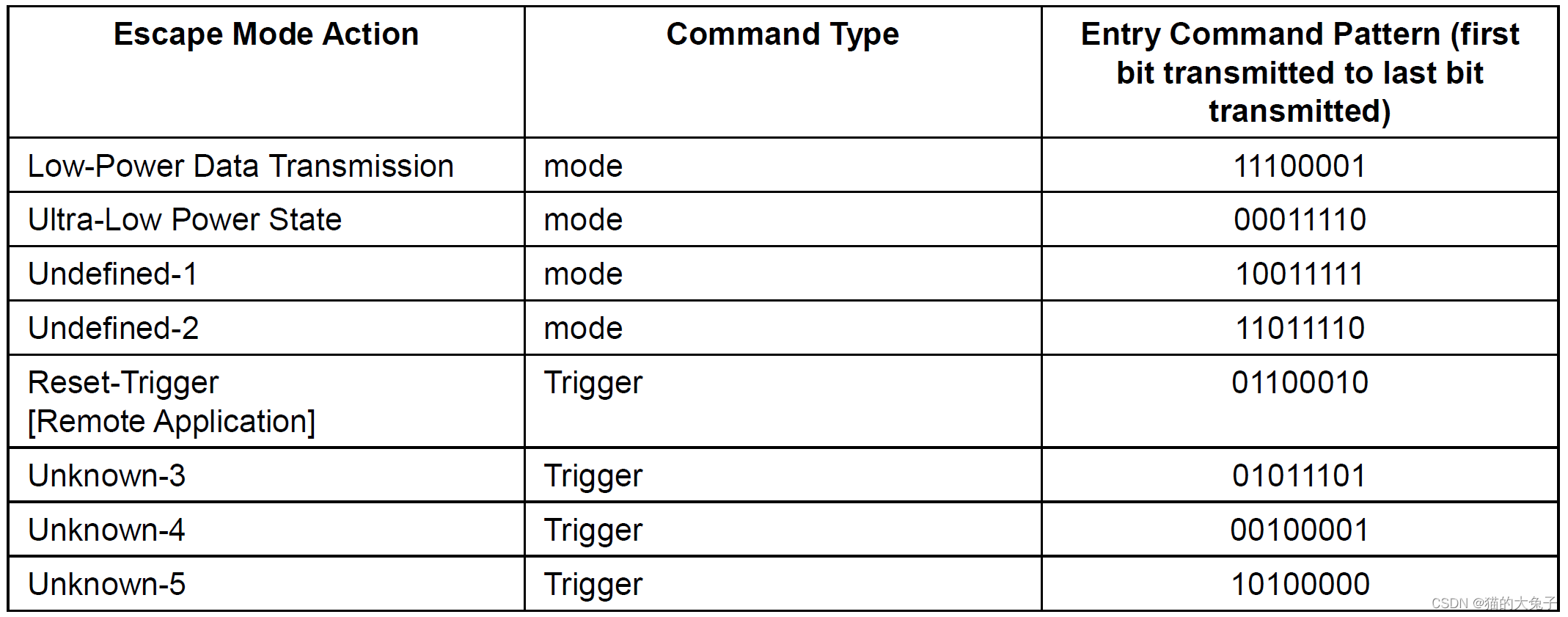

3.3.2 Escape Mode

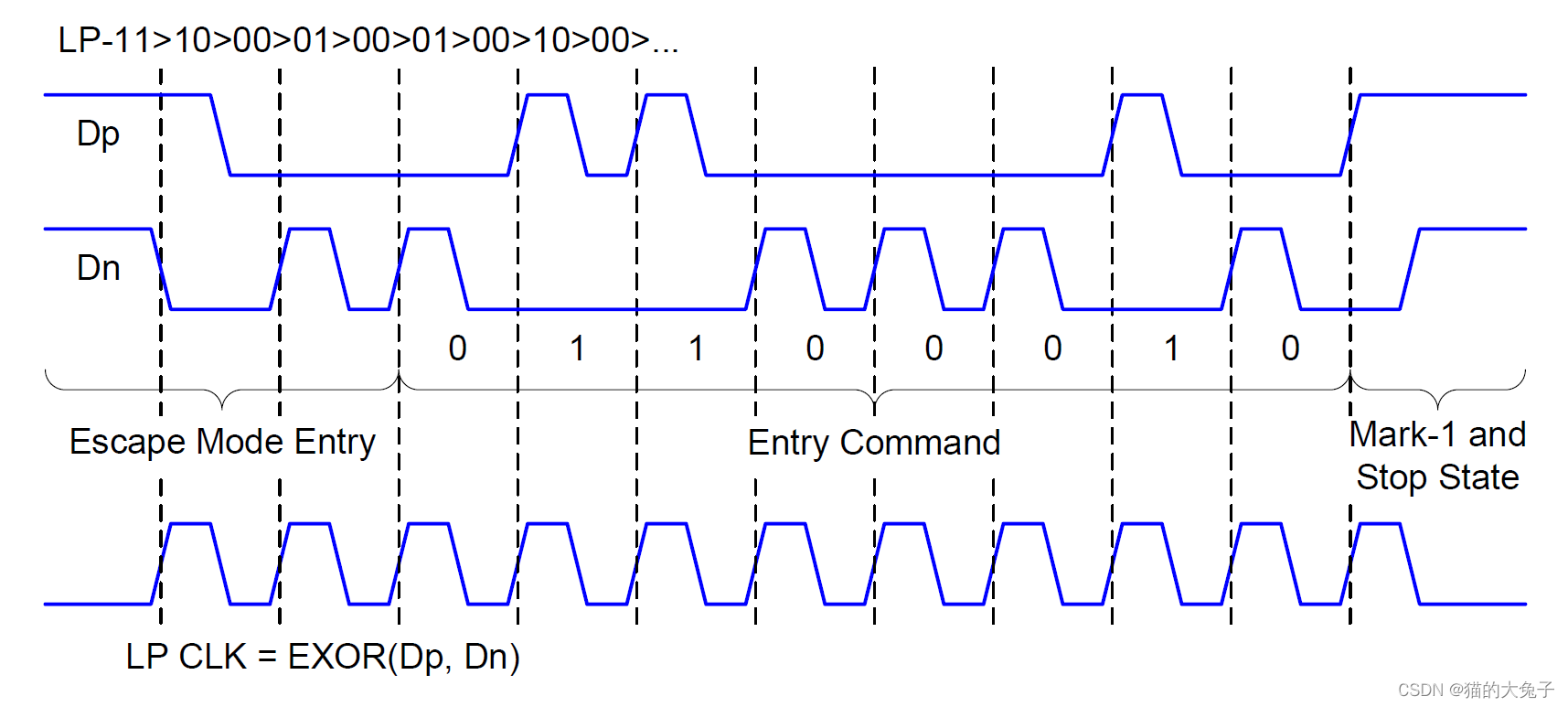

Escape Mode是Data Lane处于低功耗状态的一种特殊操作模式。在这种模式下,很多附加的操作都是可以实现的,甚至是与对端的自定义行为。如何实现这些附加操作呢==》通过Escape Entry Codes。如下图所示,目前D-PHY定义了Low-Power Data Transmission,Ultra-Low Power State 与 Reset-Trigger三种模式。在进入Escape Mode之后通过发送Escape Entry Codes,这样自己与对端都能知道要进入什么模式了。

进入Escape Mode序列:LP11-> LP10-> LP00->LP01->LP->00

退出Escape Mode序列:LP11以状态机方式来看Escape Mode下的三种情况,下图比较清晰:

3.3.2.1 Reset-Trigger

Trigger是根据发送方协议的请求向接收方协议发送标志的机制。这可以是正向或反向,具体取决于操作方向和可用的Escape Mode功能。

下图为发送一个Reset-Trigger的波形图。

Note:包括 Reset-Trigger 在内的触发信号是一个通用的消息系统。Trigger命令不会影响 PHY本身的行为。因此,协议层可以将Trigger用于任何目的。

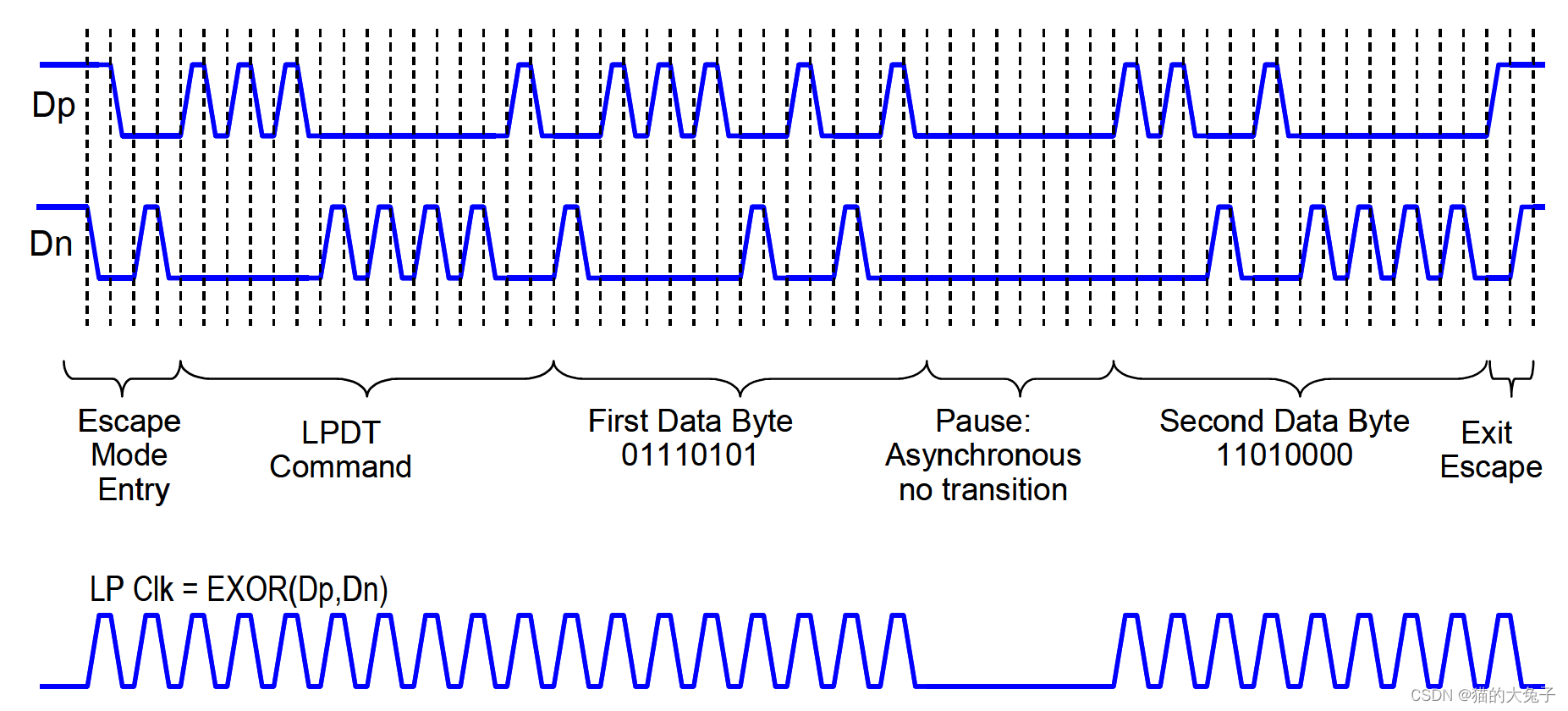

3.3.2.2 Low-Power Data Transmission

如果 Escape 模式进入程序之后是低功耗数据传输 (LPDT) 进入命令,则数据可以通过协议以低速进行通信,而通道保持在低功耗模式。

Data Lane可以在使用 LPDT 时暂停,即在保持Space state(LP00)。

数据应使用与Entry Commands相同的 Spaced-One-Hot 代码在行上进行编码。

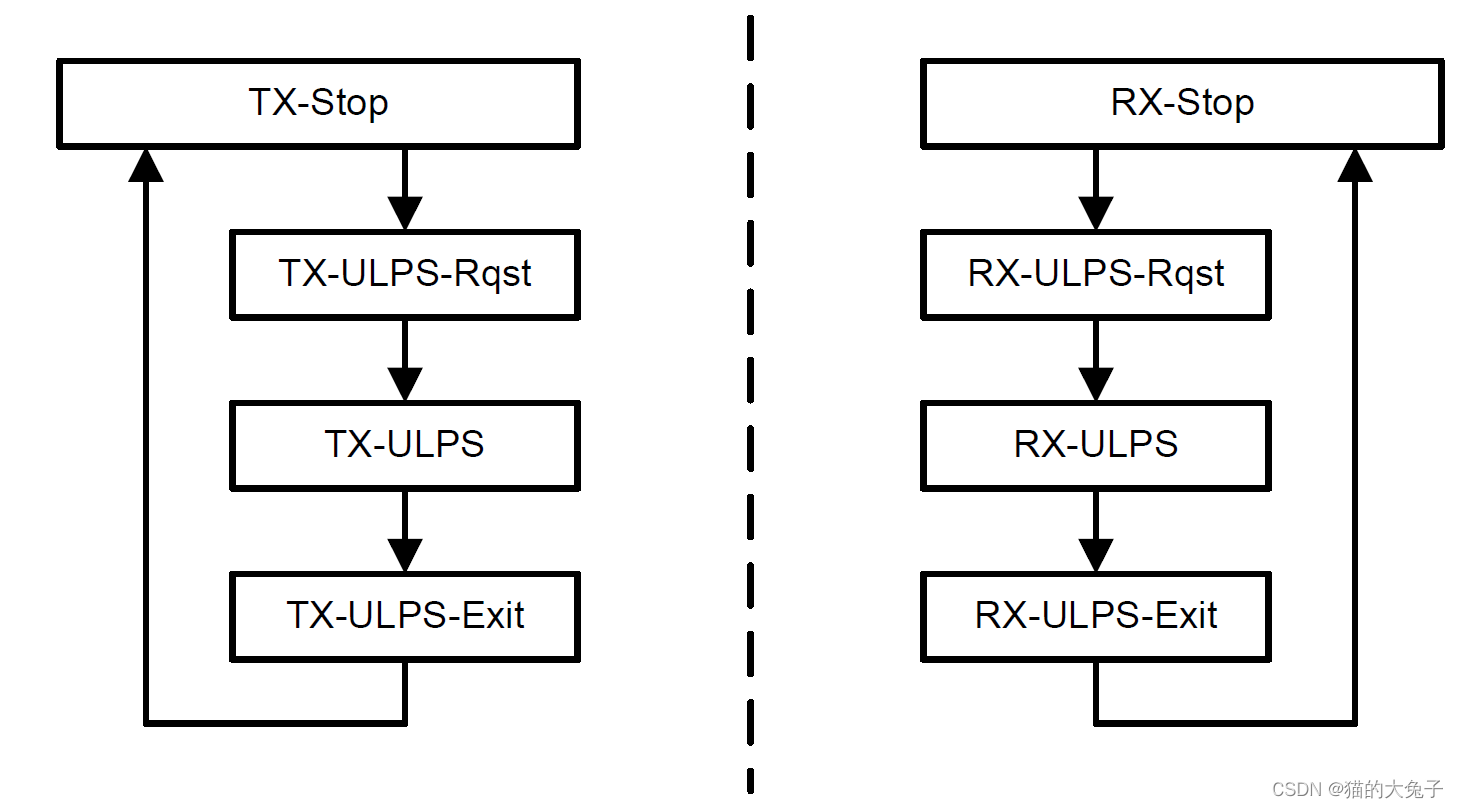

3.3.2.3 Ultra-Low Power State

如果在退出模式进入命令之后发送超低功耗状态进入命令,则通道应进入超低功耗状态 (ULPS),在此状态期间,线路处于空间状态 (LP-00)。

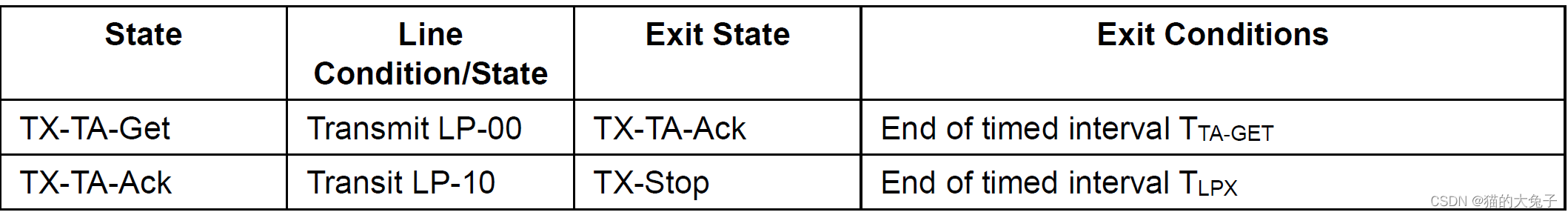

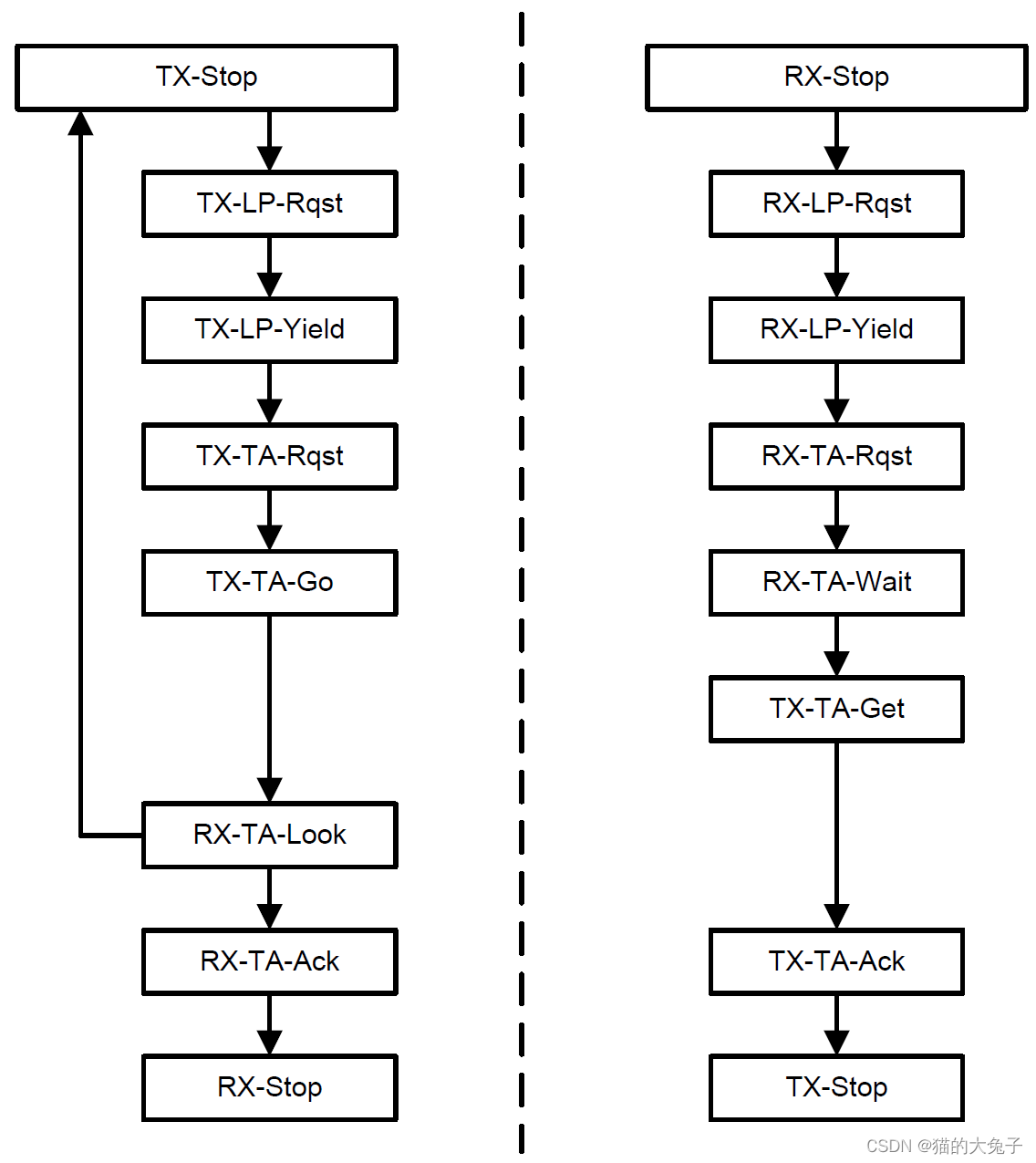

3.4 Bi-directional Data Lane Turnaround

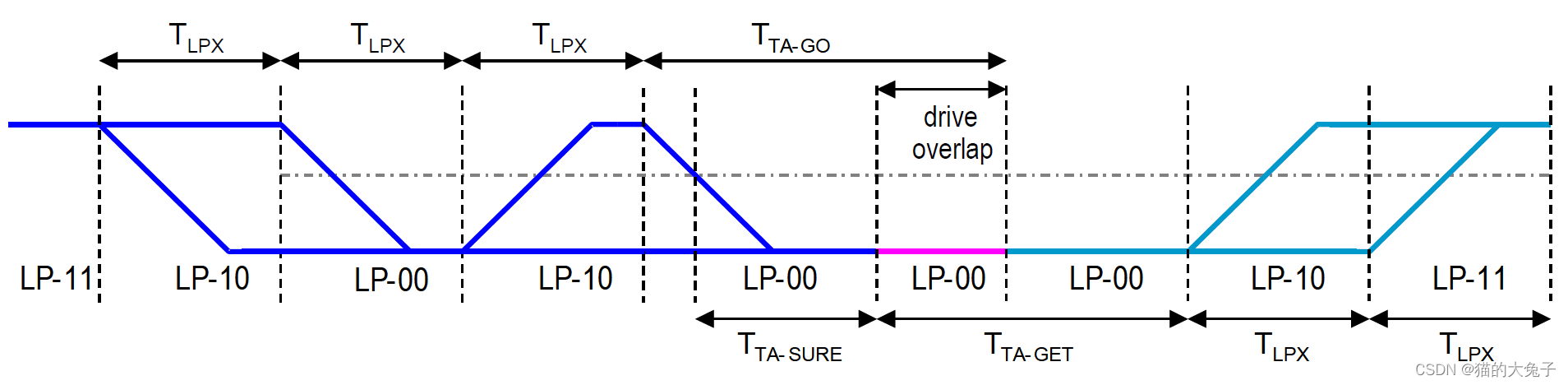

Data Lane的控制权可以通过Bus Turn Around功能来移交,即达到D-PHY半双工,Data Lane能双向传输的设计目的。但Master需要Slave发送数据的时候,首先Master处于Control Mode(LP11)下,向Slave发送BTA序列,则Slave接收之后则开始驱动总线并发送相应数据。

BTA应完全在控制模式下处理。

BTA 序列:LP11->LP10->LP-00->LP10->LP-00->Wait ACK(接收 LP-00,此时共同驱动)->Slave端 LP10->Slave端LP11;

状态机:

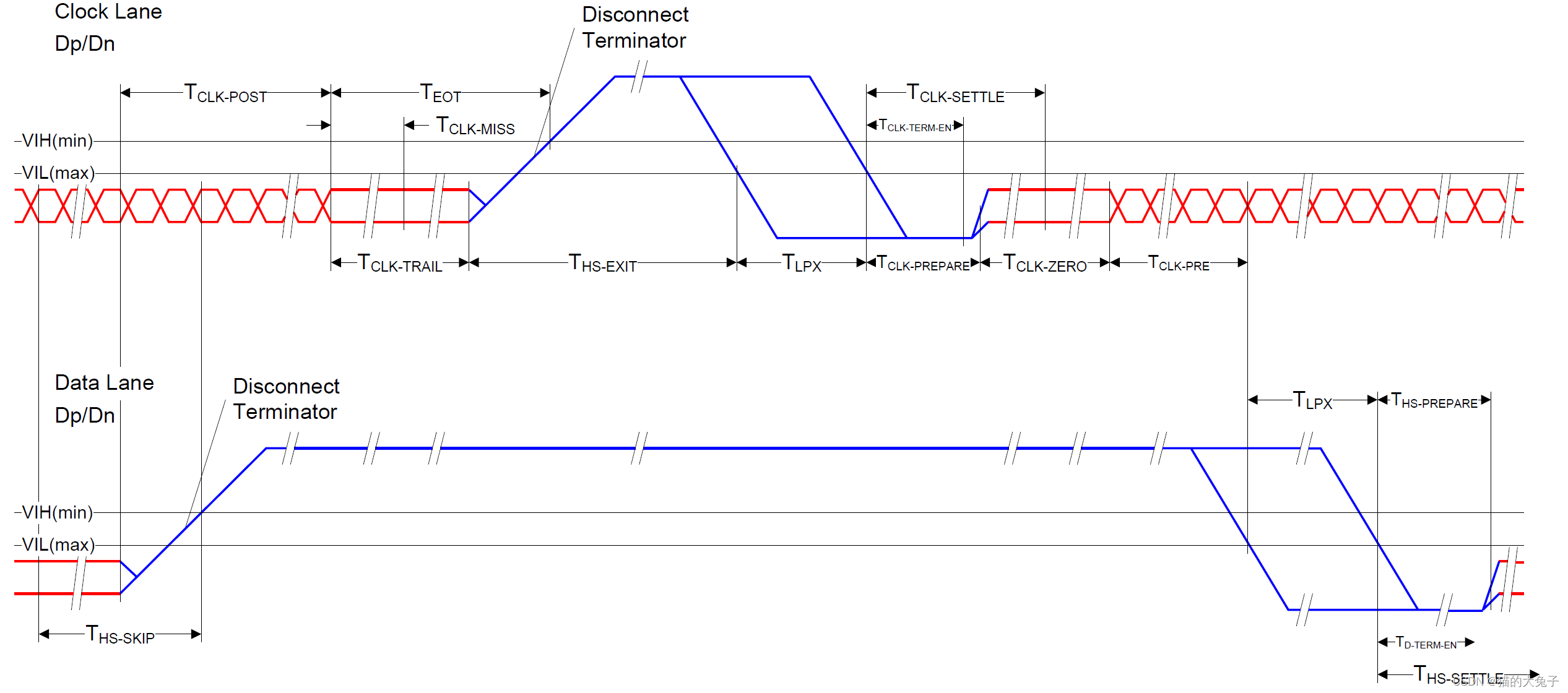

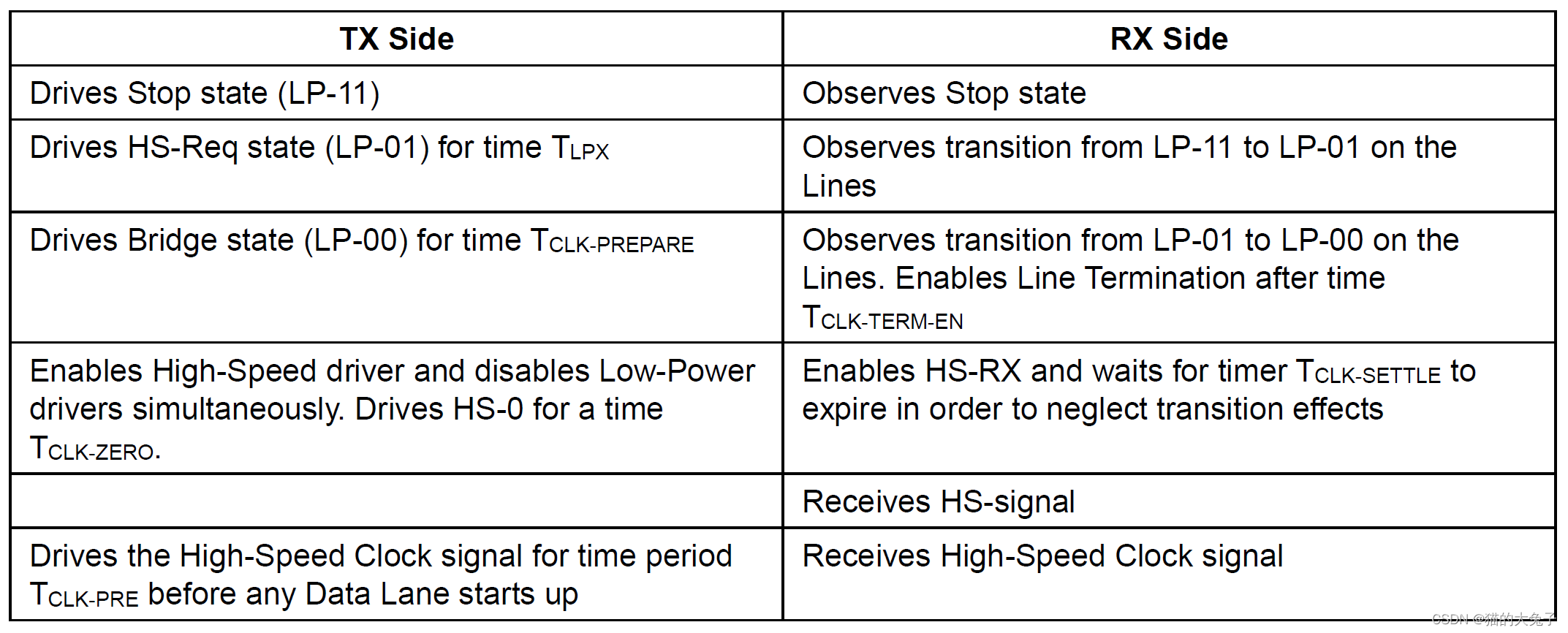

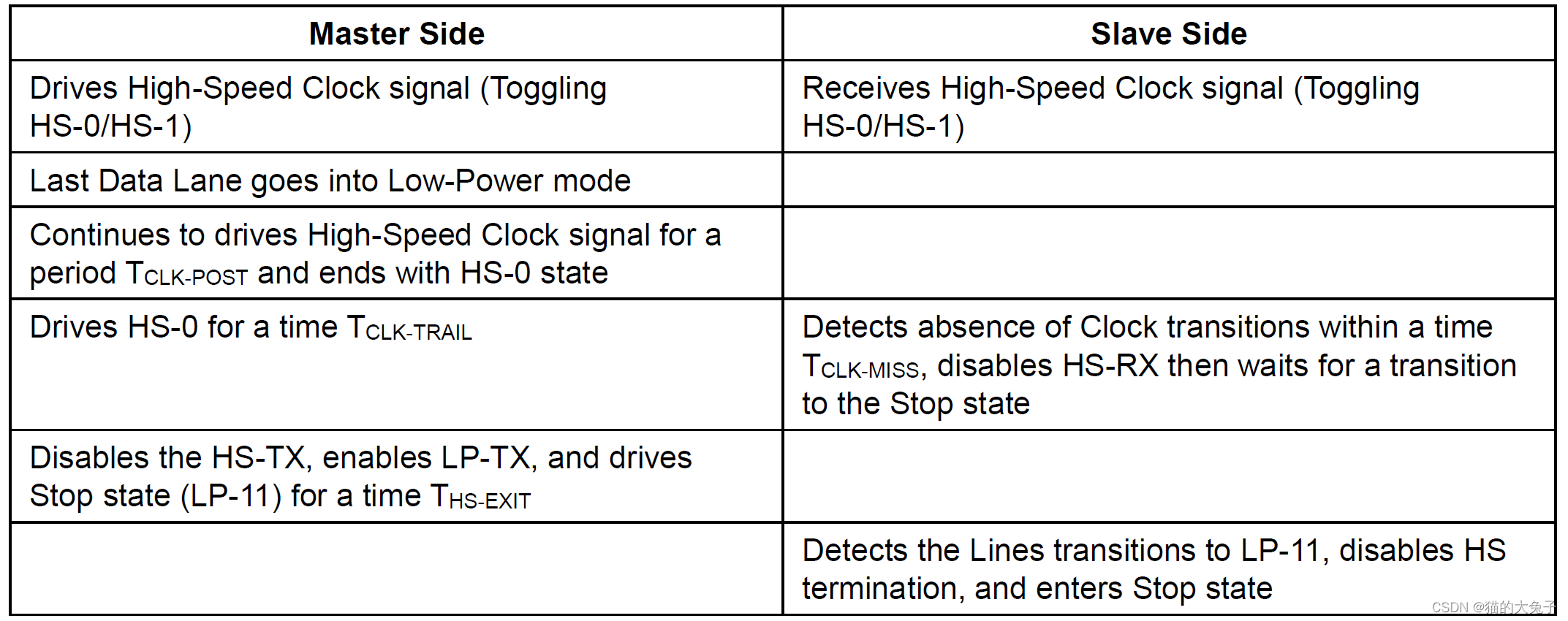

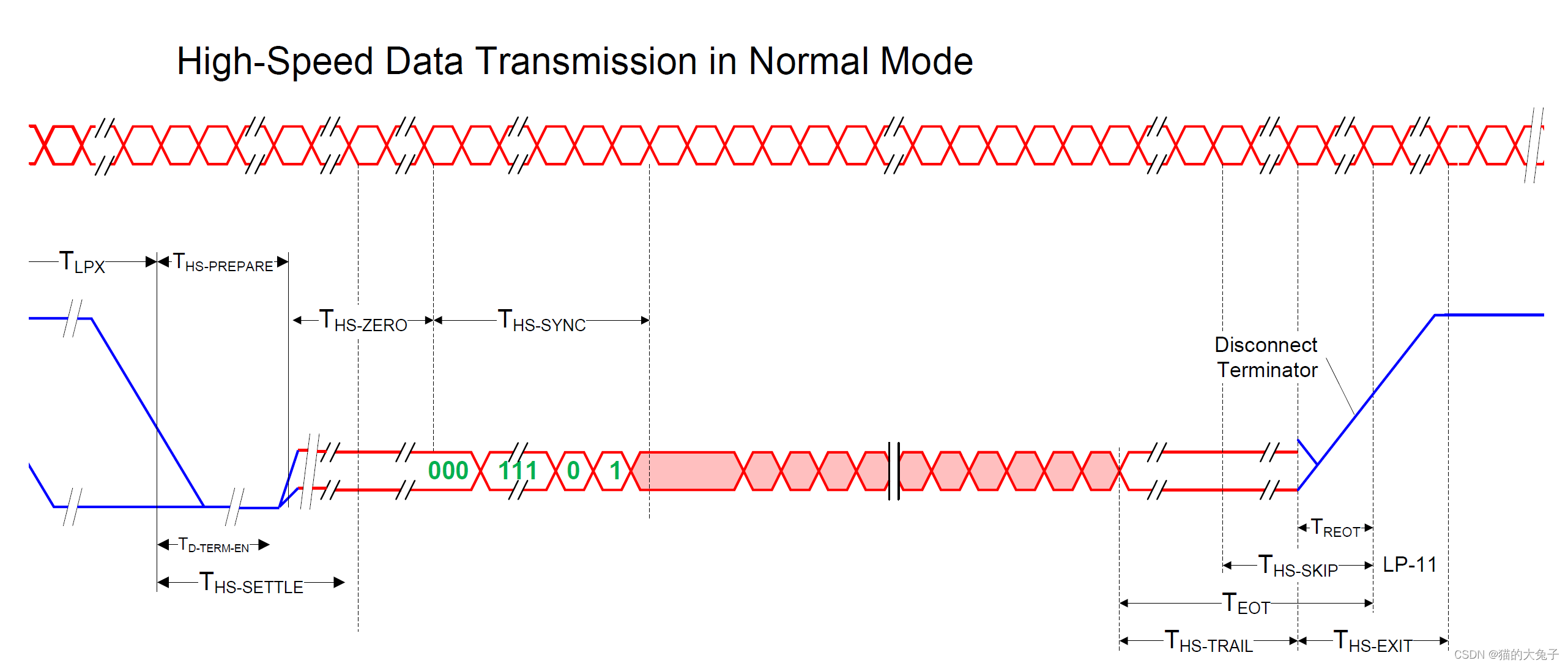

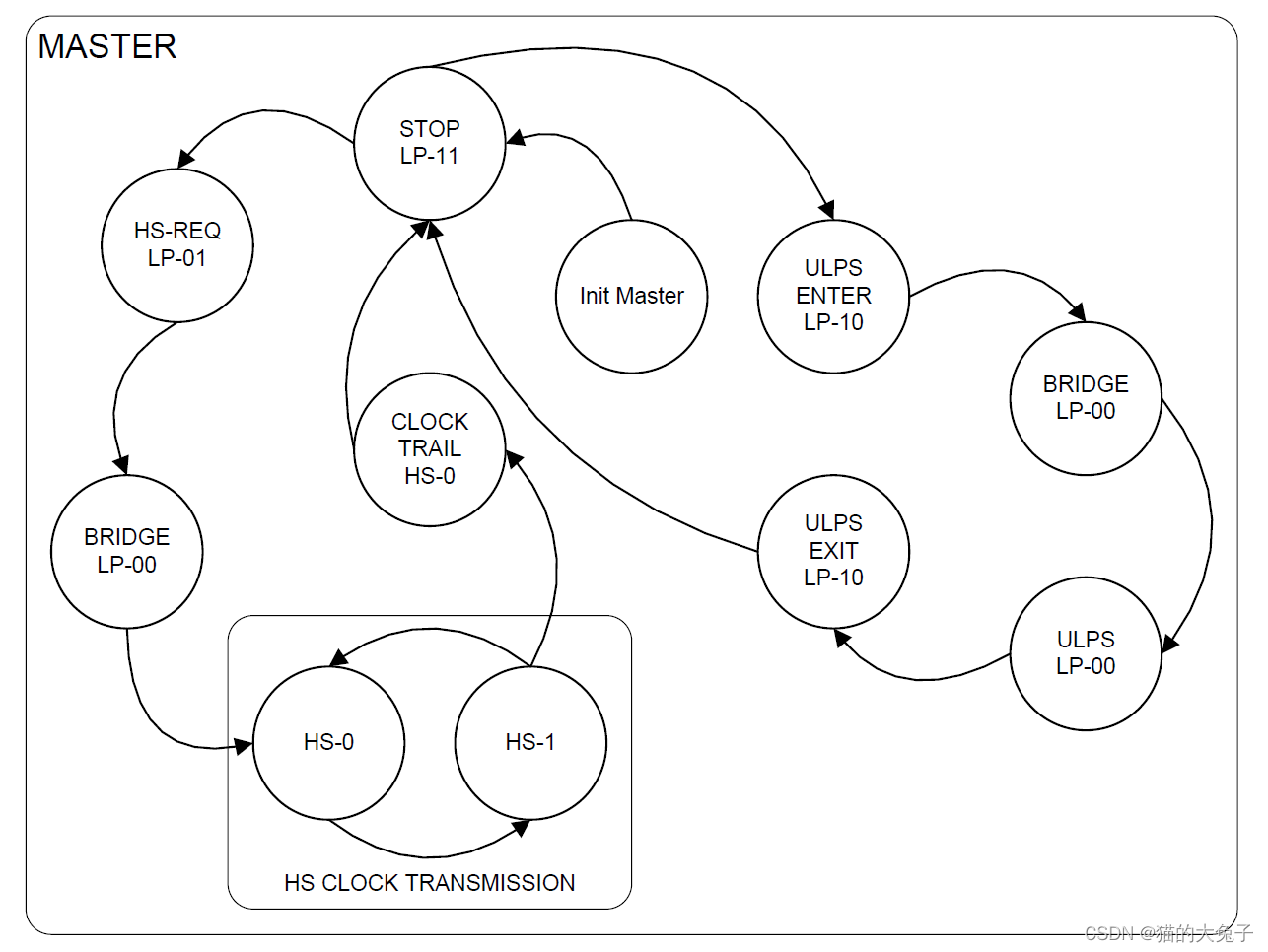

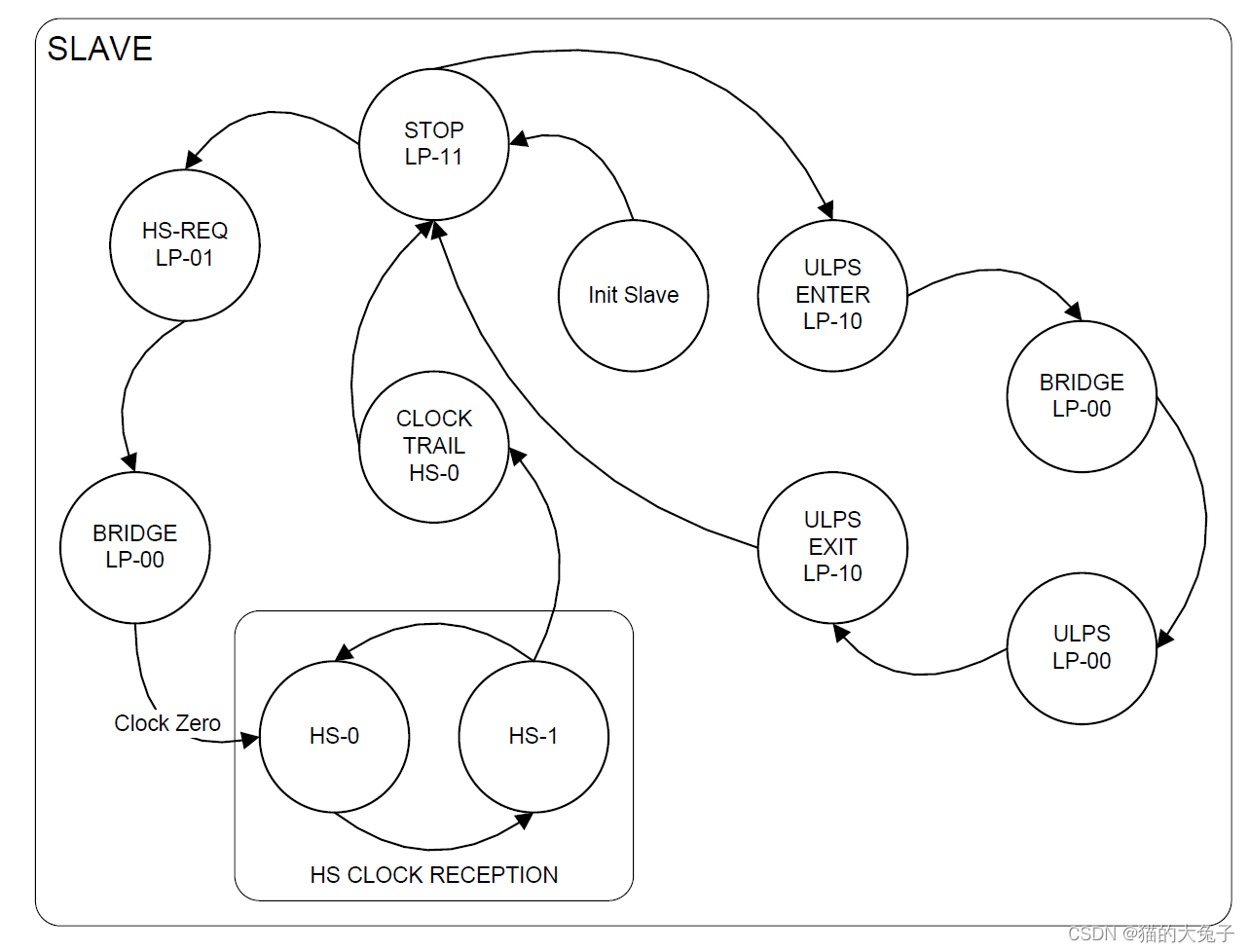

3.5 D-PHY Clock Lane High-Speed Mode

在HS模式下,Clock Lane提供从Master到Slave的低摆幅、差分 DDR(半速率)时钟信号,用于高速数据传输。Clock Lane类似于单向数据通道,只能为Master向Slave方向。

Clock Lane 进入High-Speed Mode序列:LP11->LP10(TLPX)->LP00(TCLK-PREPARE)->HS0(TCLK-ZERO)->TCLK-PRE

Clock Lane 退出High-Speed Mode序列:HS0/HS1->TCLK-POST end with HS0->TCLK-TRAIL->LP-11(THS-EXIT)进入HS:

退出HS:

状态机:

3.6 D-PHY Clock Lane ULPS Mode

虽然时钟通道不包括常规的 Escape 模式,但时钟通道应支持超低功耗状态。

Clock Lane 进入ULPS Mode序列:LP11->LP10->LP00

Clock Lane 退出ULPS Mode序列:LP00->LP10(Twakeup)->LP11

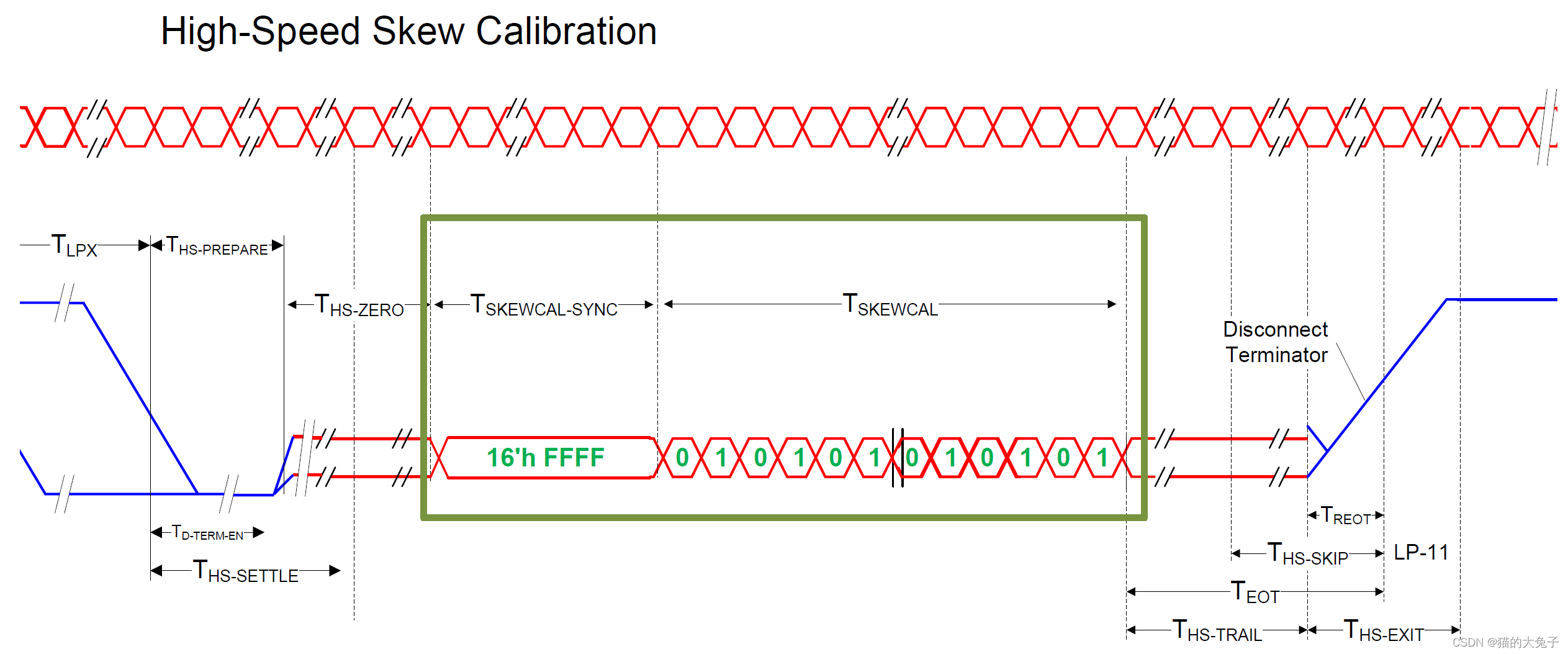

3.7 D-PHY Skew Calibration

当运行高于 1.5 Gbps 或更改为高于 1.5 Gbps 的任何速率时,需要进行Skew Calibration,以保证数据的正确传输。当速率低于1.5Gbps或者改变状态时(ULPS 到 HS),Skew Calibration是可选的。

对比如下:

Start-of-Skew Calibration 序列:LP11->LP01(TLPX)->LP00(THS-PREPARE)->HS0 (THS-ZERO)->high-speed sync sequence(16’hFFFF)->01010101 same as clock lane

End-of-Skew Calibration 序列:THS-TRAIL->LP11(THS-EXIT)

4 Fault Detection

D-PHY 有三种不同的机制来检测链路的错误。分比如如下:

- Contention Detection

- Sequence Error Detection

- Protocol Watchdog Timers (informative)

4.1 Contention Detection

Contention Detection即竞争检测。在除开特殊的过渡阶段(例如:BTA)之外,总线只能由一段驱动。由于错误或者系统错误,导致Lane处于未知状态,两端同时驱动或者同时不驱动总线,即称为总线竞争检测。

具备双向通信的 Lane,都必须具备总线竞争监测并且监测出如下冲突:

- 同一条线路两侧的模块相互驱动相反的 LP 电平。在这种情况下,线路电压将稳定在 VOL,MIN 和 VOH,MAX 之间的某个值。 因为 VIL 大于 VIHCD,所以稳定值将始终高于 VIHCD、低于 VIL,或两者兼而有之。

- 一侧的模块驱动 LP-high,而另一侧驱动同一条线上的 HS-low。在这种情况下,线路电压将稳定到低于 VIL 的值。 应在传输 LP-high 的一侧检测到争用。

第一个条件可以通过 LP-CD 和 LP-RX 功能的组合来检测。

LP-RX 功能应该能够检测到第二个争用条件。

4.2 Sequence Error Detection

Sequence Error Detection即序列错误监测。如果通道信号异常,接收 PHY 可能会检测到信号序列错误。在 PHY 内部检测到的错误可以通过 PPI 传送给协议。 这种错误检测是可选的,但强烈推荐,因为它提高了可靠性。

主要序列错误如下:

- SoT Error

- SoT Sync Error

- EoT Sync Error

- Escape Entry Command Error

- LP Transmission Sync Error

- False Control Error

4.3 Protocol Watchdog Timers (informative)

PHY 层无法监测所有错误,尤其是协议层的错误。D-PHY可以提供一个定时器,由使用者告诉D-PHY需要运行的时间,如果运行超时,则D-PHY认为这是错误。该Timeout机制来检测的行为主要如下:

- HS RX Timeout

- HS TX Timeout

- Escape Mode Timeout

- Escape Mode Silence Timeout

- Turnaround Errors

5 Global Operation Flow Diagram

版权声明:本文内容由互联网用户自发贡献,该文观点与技术仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 dio@foxmail.com 举报,一经查实,本站将立刻删除。