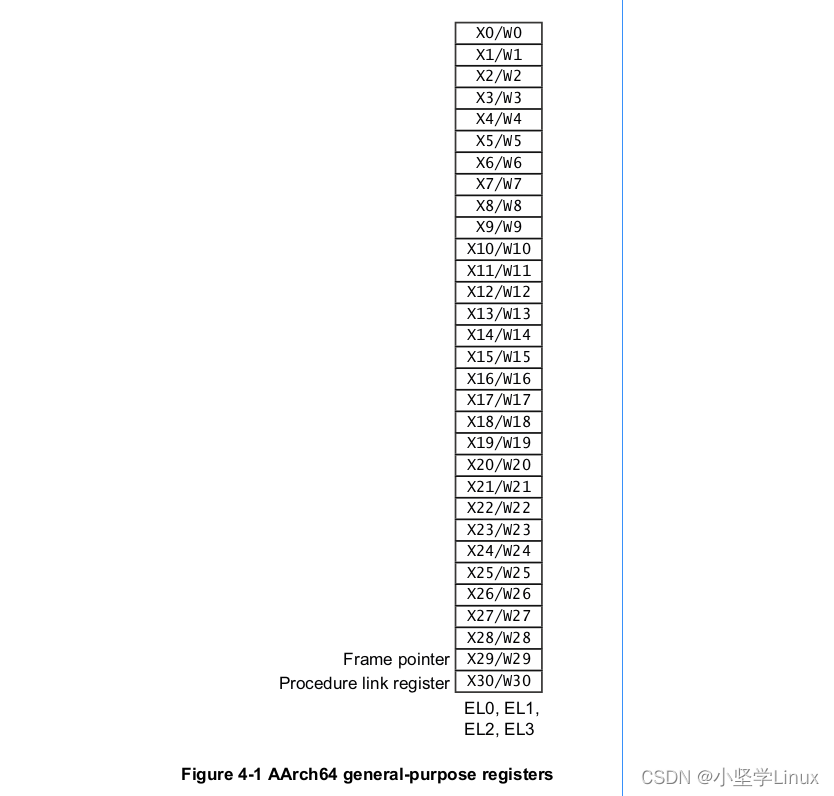

一、通用寄存器

AArch64执行状态提供了31个在任何时间任何特权级下都可访问的64位的通用寄存器。每个寄存器都有64位宽,它们通常被称为寄存器X0-X30。每个AArch64 64位通用寄存器(X0-X30)也具有32位(W0-W30)形式。每一个通用寄存器可以作为64位的通用寄存器,我们叫他们(X0-X30),也可以作为32位的通用寄存器(W0-W30)。

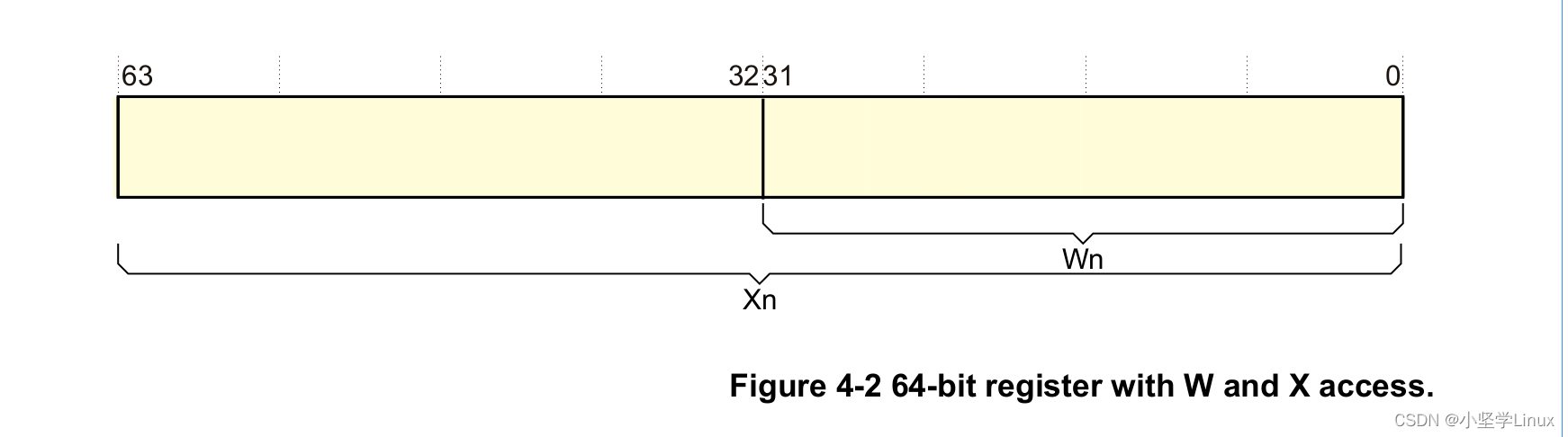

如下图所示,每一个通用寄存器都是64位的。32位寄存器(W0-W30)取自相应的64位寄存器(X0-X30)的低32位。也就是说,W0映射到X0的低32位,W1映射到X1的低32位。从32位寄存器(W0-W30)读取时,忽略相应64位寄存器(X0-X30)高32位,并保持其它不变。写入32位寄存器(W0-W30)时,将64位寄存器(X0-X30)的高32位设置为零。也就是说,将0xFFFFFFFF写入W0会将X0设置为0x00000000FFFFFFFF。

通用的寄存器一般作为用来传参。出于函数调用的目的,通用寄存器分为四组:

- x0-x7:参数寄存器

这些寄存器一般用作参数寄存器,用于传递子程序的参数和返回值,使用时不需要保存,多余的参数用堆栈传递,64位的返回结果保存在x0中。 它们也可以用作临时寄存器或调用者保存的寄存器变量,可以在函数内保存中间值,或者函数调用之间传递参数。 - X9-X15:调用者寄存器

如果调用者需要在调用另一个函数时保留一些寄存器中的任何值,则调用者必须将受影响的寄存器保存在自己的堆栈帧中。 也可以修改子例程,而不需要在返回调用函数时保存值到堆栈和从堆栈中恢复它们。 - X19-X29:被调用寄存器

这些寄存器保存在被调用者内部。 只要在返回前保存并恢复,就可以在被调用的子程序中修改。 - X8, X16-X18, X29, X30:特殊目的寄存器

X8 是间接结果寄存器。 这用于传递间接结果的地址位置,例如,函数返回大型结构的位置。

X16 和 X17 分别是 IP0 和 IP1,临时寄存器(intra-procedure-call )可以通过veneers或者类似代码使用,或者作为子程序调用之间的中间值的临时寄存器。它们可以被函数破坏。veneers代码是链接器自动插入的一小段代码,例如当分支(跳转)目标超出分支指令(支持的)范围时。

X18 是平台寄存器,保留供平台 ABI 使用。这是平台上的一个附加临时寄存器,没有为其分配特殊含义。

X29 是 Frame Pointer 寄存器,指向当前方法栈的底部。用于连接栈帧,使用时必须保存。

X30 是链接寄存器,这个寄存器会记录着当前方法的调用方地址 ,即当前方法调用完成时应该返回的位置。我们进行函数调用的时候,会用X30记录当前调用地址,等调用函数执行完毕,会从X30取出地址进行返回。我们遇到 Crash 要获取方法堆栈,其本质就是不断的向上递归每一个 x30 寄存器的记录状态(也就是栈上 X30 寄存器的内容) 来找到上层调用方。

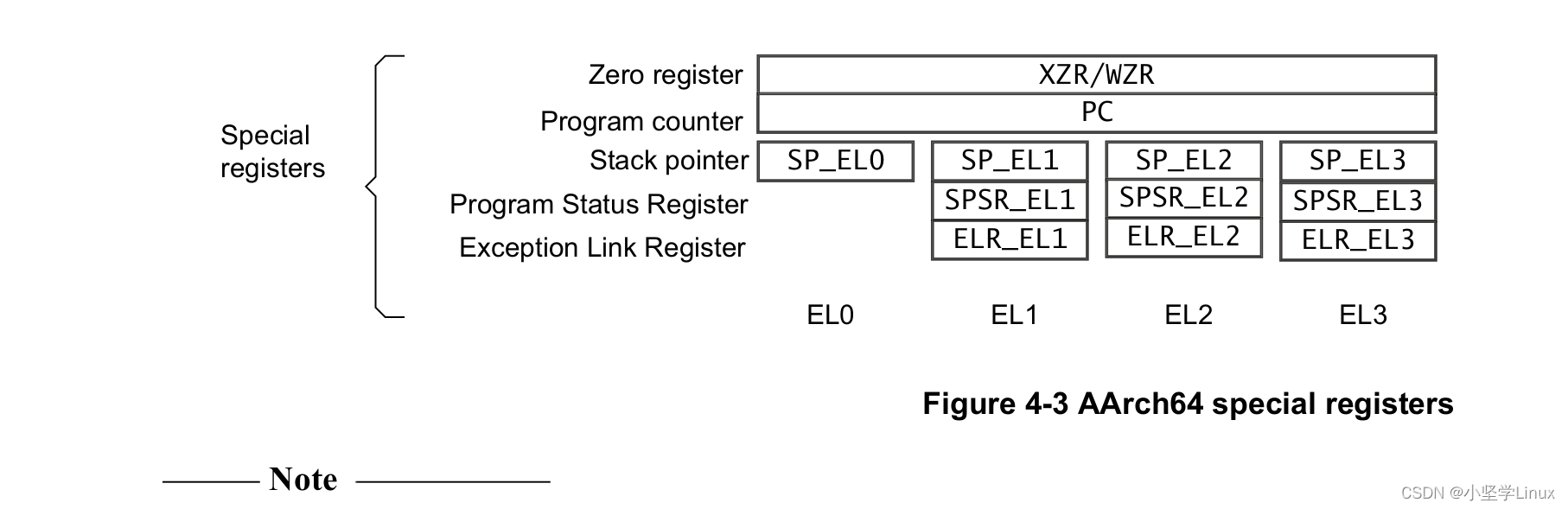

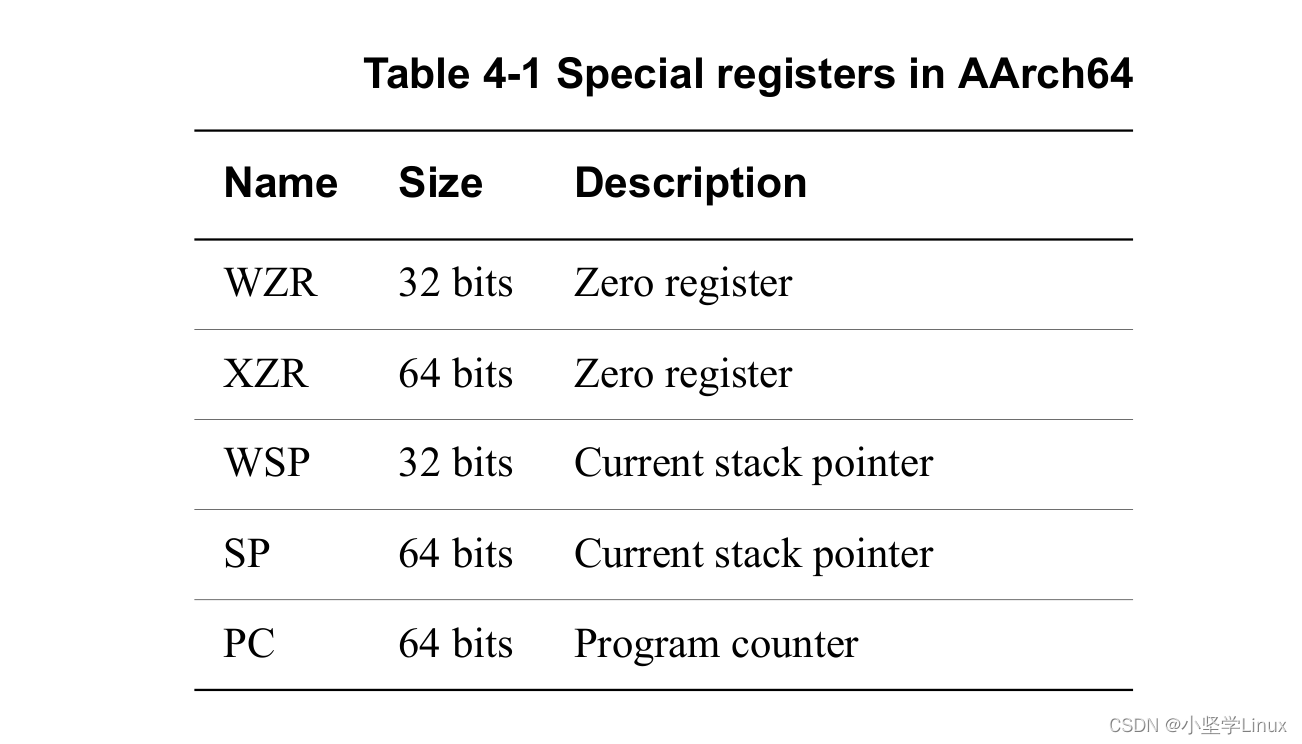

二、特殊寄存器

除了31个核心的通用寄存器外,还有几个特殊的寄存器,包括零寄存器、程序计数器、栈指针、程序状态寄存器、异常链接寄存器。其中零寄存器、程序计数器只有一个,而栈指针、程序状态寄存器、异常链接寄存器则每个异常级别都有一个。好吧,EL0没有程序状态寄存器、异常链接寄存器,因为EL0不需要保存自己的程序状态,也没有处于EL0的异常。

1.零寄存器(XZR)

当访问零寄存器时,所有写操作都被忽略,所有读操作返回0。因为操作寄存器的速度是最快的,这个寄存器的作用是提供0这个值,避免了操作内存。

零寄存器当用作源寄存器时读操作的结果为零,当用作目标寄存器时则将结果丢弃。你可以在大多数指令中但不是所有指令中使用零寄存器。

2.程序计数器(PC)

原来的ARMv7指令集的一个特性是R15作为程序计数器(PC),并作为一个通用寄存器使用。PC寄存器的使用带来了一些编程技巧,但它为编译器和复杂的流水线的设计引入了复杂性。在ARMv8中删除了对PC的直接访问,使返回预测更容易,并简化了ABI规范。

PC永远不能作为一个命名的寄存器来访问。但是,可以在某些指令中隐式的使用PC,如PC相对加载和地址生成。PC不能被指定为数据处理或加载指令的目的操作数。

3.栈指针(SP)

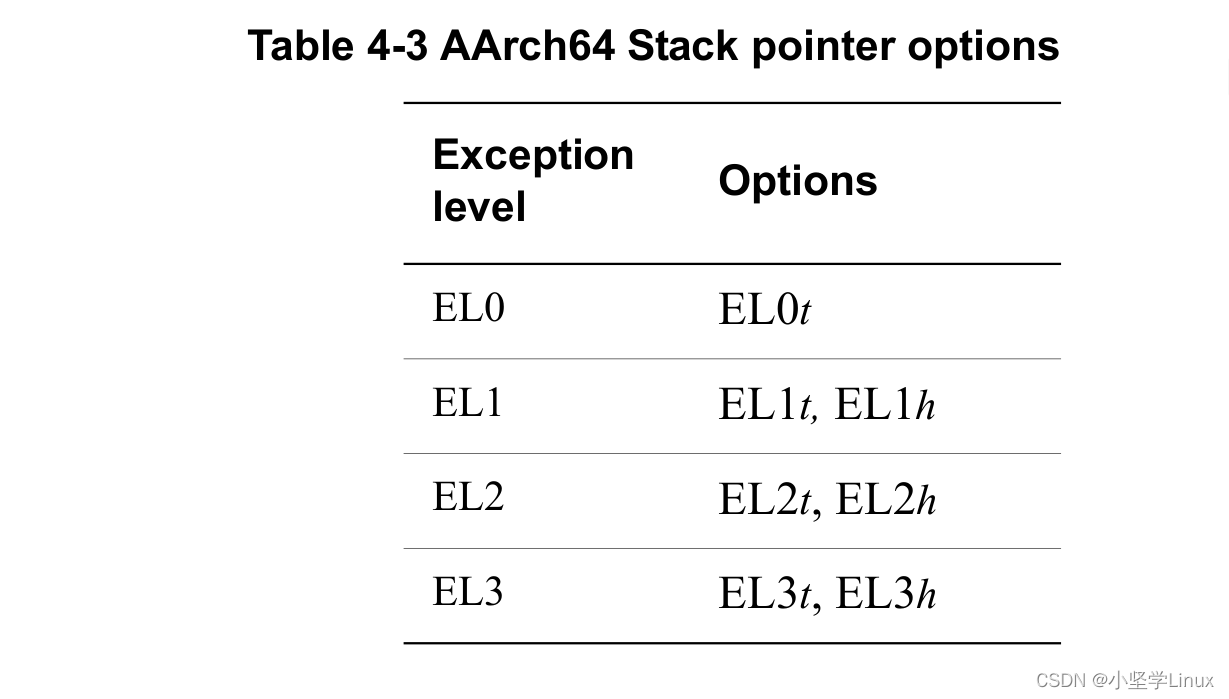

在ARMv8体系结构中,要使用的栈指针的选择在一定程度上与异常级别是分开的。默认情况下,发生异常时会选择目标异常级别的SP_ELn作为栈指针。例如,当触发到EL1的异常时,就会选择SP_EL1作为栈指针。每个异常级别都有自己的栈指针,SP_EL0、SP_EL1、SP_EL2和SP_EL3。

当AArch64处于EL0以外的异常级别时,处理器可以使用与该异常级别相关联的一个专用的64位栈指针(SP_ELn)与EL0关联的栈指针(SP_EL0)。是,EL0永远只能访问SP_EL0。

如上图所示,t后缀表示选择了SP_EL0栈指针。h后缀表示选择了SP_ELn栈指针。

虽然大多数指令都无法使用SP寄存器。但是有一些形式的算术指令可以操作SP,例如,ADD指令可以读

写当前的栈指针以调整函数中的栈指针。例如:

ADD SP, SP, #0x10 // Adjust SP to be 0x10 bytes before its current value

4.程序状态寄存器(SPSR)

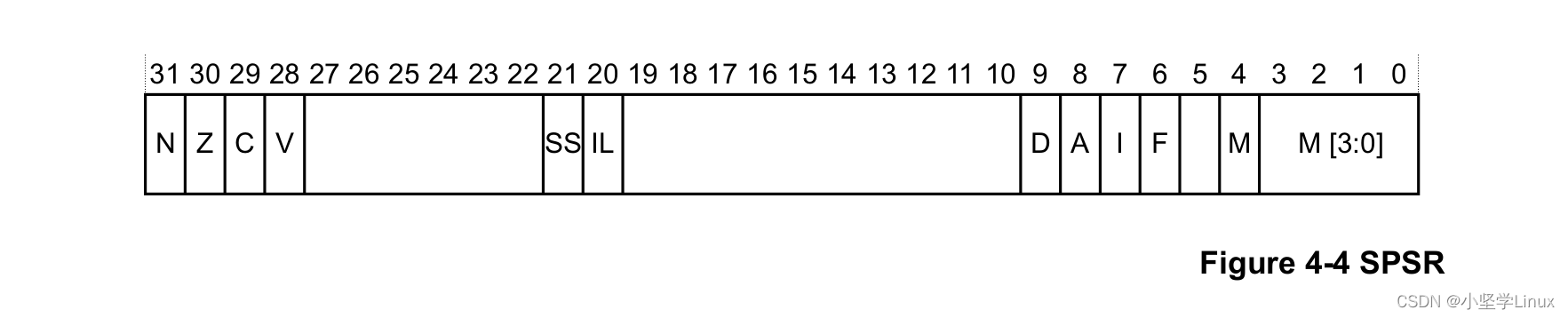

当异常发生时,cpsR中的处理器状态将保存在相关的程序状态保存寄存器(SPSR)中,其方式类似于ARMv7。SPSR保存着异常发生之前的PSTATE的值,用于在异常返回时恢复PSTATE的值。

AArch64下各bit的含义:

| bit | 含义 |

|---|---|

| N | 负数标志位,如果结果为负数,则N=1;如果结果为非负数,则N=0。 |

| Z | 零标志位,如果结果为零,Z=1,否则Z=0。 |

| C | 进位状态标志位 |

| V | 溢出状态标志位 |

| SS | 软件步进标志位 ,表示当一个异常发生时,软件步进是否开启 |

| IL | 非法执行状态位 |

| D | 程序状态调试掩码,在异常发生时的异常级别下,来自监视点、断点和软件单步调试事件中的调试异常是否被屏蔽。 |

| A | SError(系统错误)掩码位 |

| I | IRQ掩码位 |

| F | FIQ掩码位 |

| M[4] | 异常发生时的执行状态 ,0表示AArch64 |

| M[3:0] | 异常发生时的mode或异常级别 |

在ARMv8中,写入的SPSR依赖于异常级别。如果异常发生在EL1,则使用SPSR_EL1。如果异常发生在EL2,则使用SPSR_EL2,如果异常发生在EL3,则使用SPSR_EL3。处理器核会在异常发生时填充SPSR。

5.异常链接寄存器(ELR)

异常链接寄存器保存异常返回地址。异常包括Serror,iqr和fiq。举个例子,cpu通过irq从el1陷入到el2的时候会把el1的pc保存到ELR寄存器中,当cpu从el2返回的时候,从ELR寄存器取出pc值继续运行。

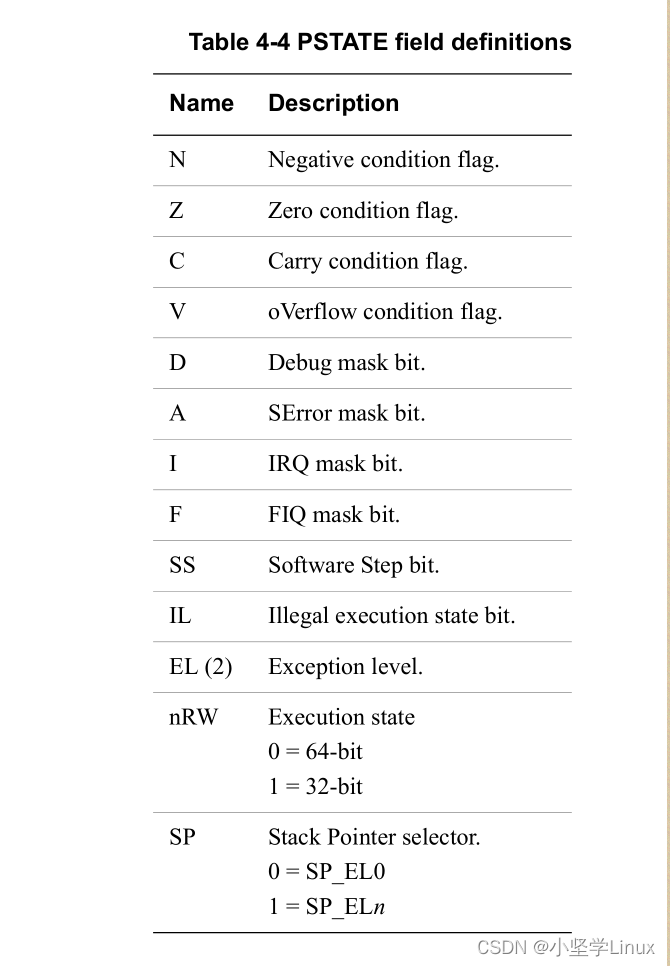

三、处理器状态寄存器

AArch64没有直接与ARMv7当前程序状态寄存器(cpsR)等价的寄存器。在AArch64中,传统cpsR的组件作为可以独立访问的字段提供。这些状态被统称为处理器状态(PSTATE)。下图中,PSTATE.{N, Z, C, V}字段可以在EL0级别访问。 其他的字段可以在EL1或更高级别访问,但是这些字段在EL0级别未定义。

在AArch64中,你可以通过执行ERET指令从一个异常中返回,这将导致SPSR_ELn被复制到PSTATE中。这将恢复ALU标志、执行状态、异常级别和处理器分支。从这里开始,将继续从ELR_ELn中的地址开始执行。

四、系统寄存器

在AArch64中,系统配置通过系统寄存器进行控制,并使用MSR和MRS指令进行访问。这与ARMv7-A形成了鲜明对比,在ARMv7-A中,这些寄存器通常通过协处理器15(CP15)操作来访问。寄存器的名称会告诉你可以访问它的最低异常级别。具有后缀_ELn的系统寄存器在各异常级别中有一个独立的的副本,但通常不是EL0,很少有系统寄存器可以从EL0访问,尽管缓存类型寄存器(CTR_EL0)是一个可以从EL0访问的系统寄存器的例子。

举个例子,可以采用以下形式来访问系统寄存器:

MRS x0, TTBR0_EL1 // Move TTBR0_EL1 into x0

MSR TTBR0_EL1, x0 // Move x0 into TTBR0_EL1

ARM体系结构以前的版本使用协处理器来进行系统配置。但是,AArch64并不包含对协处理器的支持。这里会介绍一些比较重要的寄存器,如果想查看全部,请参见ARM体系结构参考手册-ARMv8的附录J查看完整的列表。下面介绍一下系统控制寄存器及其功能:

| 寄存器 | 名称 | 功能 |

|---|---|---|

| CTR_EL0 | 缓存寄存器 | 与cpu缓存信息相关 |

| ID_AA64ISAR0_EL1 | 指令实现寄存器 | |

| TCR_ELx | 翻译控制寄存器 | 用来控制MMU使用页表相关;x=1或者2 |

| SCTLR_ELx | 系统控制寄存器 | 用来控制mmu、缓存、对齐检查等ARM架构特性相关的特性 ,x=1或者2或者3 |

| HCR_EL2 | 虚拟化配置寄存器 | 用来保存控制虚拟化状态,只能EL2使用 |

| SCR_EL3 | 安全配置寄存器 | 用来保存控制安全状态,只能EL3使用 |

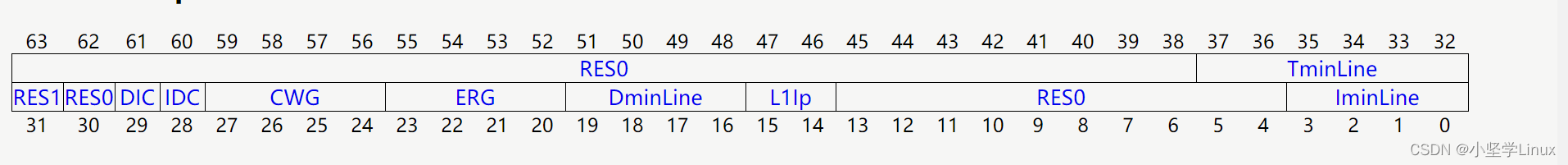

1.缓存寄存器(CTR_EL0)

缓存寄存器(CTR)是一个提供有关缓存架构的信息的寄存器,硬件上只有一个,就是CTR_EL0,所有特权和非特权状态都是访问他。

| 位数 | 名称 | 含义 |

|---|---|---|

| 63:38 | RES0 | 保留的 |

| 37:32 | TminLine | 标签最低线。在所有可以包含由PE控制的分配标签的缓存中,最小的缓存行中分配标签所覆盖的大小为2的n次方,单位为4字节。 |

| 31 | RES1 | 保留的 |

| 30 | RES0 | 保留的 |

| 29 | DIC | 指令缓存无效要求数据与指令一致性。0: 数据与指令的一致性,需要指令缓存失效到统一点。1:指令缓存失效到统一点,不需要数据到指令一致性。 |

| 28 | IDC | 数据缓存清理要求指令数据一致性。0:数据缓存清理到统一点是要求指令的数据一致性;1:数据缓存清理到统一点是不需要指令的数据一致性。 |

| 27:24 | CWG | 回写缓存颗粒。当缓存条目中的某个内存位置被修改后,删除该缓存条目可以覆盖的最大内存大小为2的n次方。 |

| 23:20 | ERG | 独占保留粒度,保留粒度的最大大小为2的n次方,单位4字节 |

| 19:16 | DminLine | PE控制的所有数据缓存和统一缓存中最小的缓存行大小为2的n次方,单位4字节 |

| 15:14 | L1Ip | 一级指令缓存策略。指示L1指令缓存的索引和标记策略。00:只有FEAT_VPIPT被实现才能用;01:使用ASID+虚拟地址索引域和虚拟地址的标记域;10:使用虚拟地址的索引域和物理地址的标记域;11:使用物理地址的索引域和物理地址的标记域 |

| 13:4 | RES0 | 保留的 |

| 3:0 | IminLine | 由PE控制的所有指令缓存中最小的缓存行大小为2的n次方,单位为4字节 |

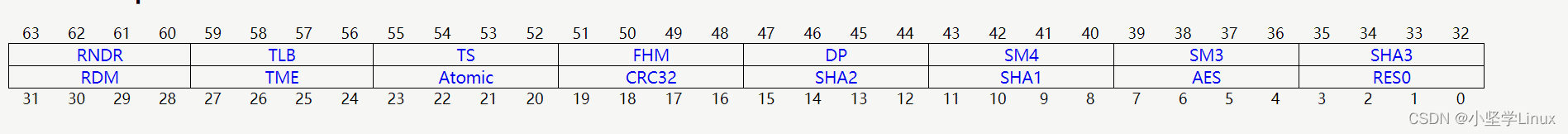

2.指令实现寄存器(ID_AA64ISAR0_EL1)

指令实现寄存器是一个介意提供关于在AArch64状态下实现的指令的信息的寄存器。

| 位数 | 名称 | 含义 |

|---|---|---|

| 63:60 | RNDR | 表示在AArch64状态下支持随机数指令。0000:不执行随机数指令;0001:实现RNDR和RNDRRS寄存器;其他值保留 |

| 59:56 | TLB | 表示支持外层共享和TLB范围维持指令。0000: 不支持;0001:支持外部共享TLB;0010:支持外部共享和TLB范围维持;其他值保留 |

| 55:52 | TS | 表示支持标志操作指令。0000:没有实现标志操作指令;0001:实现CFINV, RMIF, SETF16和SETF8指令;0010:实现CFINV, RMIF, SETF16, SETF8,AXFLAG和xflag指令 |

| 51:48 | FHM | 表示支持FMLAL和FMLSL指令。0000:不支持;0001:支持 |

| 47:44 | DP | 表示支持AArch64状态下的点积指令。0000:不支持;0001:支持UDOT和SDOT点积指令 |

| 43:40 | SM4 | 表示支持AArch64状态下的SM4指令。0000:不支持;0001:支持SM4E和SM4EKEY指令 |

| 39:36 | SM3 | 表示支持AArch64状态下的SM3指令。0000:不支持;0001:支持SM3SS1, SM3TT1A, SM3TT1B, SM3TT2A, SM3TT2B, SM3PARTW1和SM3PARTW2指令 |

| 35:32 | SHA3 | 表示支持AArch64状态下的SHA3指令。0000:不支持;0001:支持EOR3, RAX1, XAR和BCAX指令 |

| 31:28 | RDM | 表示支持AArch64状态下的RDM指令。0000:不支持;0001:支持SQRDMLAH和SQRDMLSH指令 |

| 27:24 | TME | 表示支持AArch64状态下的TME指令。0000:不支持;0001:支持TCANCEL, TCOMMIT, TSTART和TTEST指令 |

| 23:20 | Atomic | 表示支持AArch64状态下的Atomic指令。0000:不支持;0001:支持LDADD, LDCLR, LDEOR, LDSET, LDSMAX, LDSMIN, LDUMAX, LDUMIN, CAS, CASP和SWP指令 |

| 19:16 | CRC32 | 表示支持AArch64状态下的CRC32指令。0000:不支持;0001:支持CRC32B, CRC32H, CRC32W, CRC32X, CRC32CB, CRC32CH, CRC32CW和CRC32CX指令 |

| 15:12 | SHA2 | 表示支持AArch64状态下的SHA2指令。0000:不支持;0001:支持SHA256H, SHA256H2, SHA256SU0和SHA256SU1指令;0010:支持SHA256H, SHA256H2, SHA256SU0,SHA256SU1,SHA512H, SHA512H2, SHA512SU0和SHA512SU1指令 |

| 11:8 | SHA1 | 表示支持AArch64状态下的SHA1指令。0000:不支持;0001:支持SHA1C, SHA1P, SHA1M, SHA1H, SHA1SU0和SHA1SU1指令 |

| 7:4 | AES | 表示支持AArch64状态下的AES指令。0000:不支持;0001:支持AESE, AESD, AESMC和AESIMC指令;0010:支持AESE, AESD, AESMC,AESIMC和PMULL/PMULL2指令 |

| 3:0 | RES0 | 保留的 |

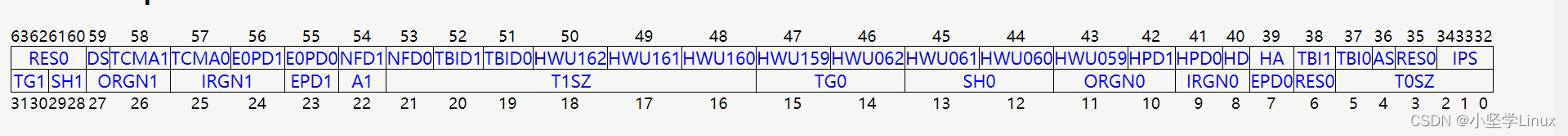

3.翻译控制寄存器(TCR_ELx)

翻译控制寄存器是第1阶段翻译状态的控制寄存器,包括TCR_EL1、 TCR_EL2和 TCR_EL3。AArch64系统寄存器TCR_EL1位[31:0]在架构上映射到AArch32系统寄存器TTBCR[31:0]。AArch64系统寄存器TCR_EL1位[63:32]在架构上映射到AArch32系统寄存器TTBCR2[31:0]。AArch64系统寄存器TCR_EL2位[31:0]在架构上映射到AArch32系统寄存器HTCR[31:0]。

TCR_EL1:

EL1&0都是用TCR_EL1寄存器。

| 位数 | 名称 | 含义 |

|---|---|---|

| 63:60 | RES0 | 保留的 |

| 59 | DS | 当在翻译制度的第1阶段使用4KB和16KB翻译粒时,该字段影响52位输出寻址,包括翻译描述符、块描述符、页描述符的输出情况 |

| 58 | TCMA1 | 控制未检查访问的生成, 0:对EL1上未检查访问是不会影响其他。1:在EL1的所有访问都是未检查的。 |

| 57 | TCMA0 | 控制未检查访问的生成, 0:对EL0上未检查访问是不会影响其他。1:在EL0的所有访问都是未检查的。 |

| 56 | E0PD1 | 对由TTBR1_EL1转换的任何地址的非特权访问的故障控制。 0:对由TTBR1_EL1转换的任何地址的非特权访问都不会产生错误;1:对由TTBR1_EL1转换的任何地址的无特权访问将产生0级转换错误。 |

| 55 | E0PD0 | 对由TTBR1_EL0转换的任何地址的非特权访问的故障控制。 0:对由TTBR1_EL0转换的任何地址的非特权访问都不会产生错误;1:对由TTBR1_EL0转换的任何地址的无特权访问将产生0级转换错误。 |

| 54 | NFD1 | 该位控制是否对使用TTBR1_EL1转换的虚拟地址进行无错误的非特权访问,以响应是否执行阶段1转换表遍历。0:不禁用使用TTBR1_EL1的阶段1翻译表遍历;1:使用TTBR1_EL1转换的虚拟地址上的TLB错过会导致访问失败,而不会发生异常。不执行第1阶段的翻译表行走 |

| 53 | NFD1 | 该位控制是否对使用TTBR0_EL1转换的虚拟地址进行无错误的非特权访问,以响应是否执行阶段1转换表遍历。0:不禁用使用TTBR0_EL1的阶段1翻译表遍历;1:使用TTBR0_EL1转换的虚拟地址上的TLB错过会导致访问失败,而不会发生异常。不执行第1阶段的翻译表行走 |

| 52 | TBID1 | 使用指令地址的顶部字节进行地址匹配控制 。0:TCR_EL1.TBI1适用于指令访问和数据访问;1:TCR_EL1.TBI1仅适用于数据访问。 |

| 51 | TBID0 | 使用指令地址的顶部字节进行地址匹配控制 。0:TCR_EL1.TBI0适用于指令访问和数据访问;1:TCR_EL1.TBI0仅适用于数据访问。 |

| 50 | HWU162 | TTBR1_EL1进行翻译的阶段1的时候,翻译表块或页条目的位[62]能否实现定义的硬件使用。0:不能;1:可以 |

| 49 | HWU161 | TTBR1_EL1进行翻译的阶段1的时候,翻译表块或页条目的位[61]能否实现定义的硬件使用。0:不能;1:可以 |

| 48 | HWU160 | TTBR1_EL1进行翻译的阶段1的时候,翻译表块或页条目的位[60]能否实现定义的硬件使用。0:不能;1:可以 |

| 47 | HWU159 | TTBR1_EL1进行翻译的阶段1的时候,翻译表块或页条目的位[59]能否实现定义的硬件使用。0:不能;1:可以 |

| 46 | HWU062 | TTBR0_EL1进行翻译的阶段1的时候,翻译表块或页条目的位[62]能否实现定义的硬件使用。0:不能;1:可以 |

| 45 | HWU061 | TTBR0_EL1进行翻译的阶段1的时候,翻译表块或页条目的位[61]能否实现定义的硬件使用。0:不能;1:可以 |

| 44 | HWU060 | TTBR0_EL1进行翻译的阶段1的时候,翻译表块或页条目的位[60]能否实现定义的硬件使用。0:不能;1:可以 |

| 43 | HWU059 | TTBR0_EL1进行翻译的阶段1的时候,翻译表块或页条目的位[59]能否实现定义的硬件使用。0:不能;1:可以 |

| 42 | HPD1 | 分级权限禁用,影响TTBR1 EL1指向的翻译表中的一些控制位。0:启用分级权限;1:禁用分级权限 |

| 41 | HPD10 | 分级权限禁用,影响TTBR0 EL1指向的翻译表中的一些控制位。0:启用分级权限;1:禁用分级权限 |

| 40 | HD | 从EL0和EL1转换阶段1脏态的硬件管理。 0:禁用脏状态的阶段1硬件管理;1:启用脏状态的阶段1硬件管理 |

| 39 | HA | 从EL0和EL1翻译的阶段1硬件访问标志更新。 0:阶段1访问标志位更新被禁用;1:阶段1访问标志位更新启用。 |

| 38 | TBI1 | 最高字节忽略。 0:地址计算中使用的Top字节匹配TTBR1_EL1区域的地址;1:地址计算中忽略的Top字节 |

| 37 | TBI0 | 最高字节忽略。 0:地址计算中使用的Top字节匹配TTBR0_EL1区域的地址;1:地址计算中忽略的Top字节 |

| 36 | AS | ASID大小。0:8位,除了回读寄存器外,TTbro_ELT和TTBR1_EL1的高8位被硬件忽略;1:16位,TTbro_EL1和TTBR1_EL1的高16位用于在TLB中分配和匹配。 |

| 35 | RES0 | 保留的 |

| 34:32 | IPS | 中间物理地址大小。000:32位,4GB;001:36位,64GB;010:40位,1TB;011:42位,4TB;100:44位,16TB;101:48位,256TB;110:52位,4PB |

| 31:30 | TG1 | TTBR1_EL1的颗粒大小。01:16KB;10:4KB;11:64Kb |

| 29:28 | SH1 | 与使用TTBR1_EL1的翻译表有关的内存的可共享性属性。00:不共享;10:外部可共享;11:内部可共享 |

| 27:26 | ORGN1 | 与使用TTBR1_EL1的翻译表有关的内存的外部缓存属性。00:不缓存;01:写回的读写缓存;10:写穿的读缓存写不缓存;11:写回的读缓存写不缓存 |

| 25:24 | IRGN1 | 与使用TTBR1_EL1的翻译表有关的内存的内部缓存属性。00:不缓存;01:写回的读写缓存;10:写穿的读缓存写不缓存;11:写回的读缓存写不缓存 |

| 23 | EPD1 | 控制是否在TLB miss上对使用TTBR1_EL1进行转换的地址执行转换表遍历。0:使用TTBR1_EL1执行翻译表遍历;1:不执行翻译表遍历 |

| 22 | A1 | 选择是否是TTBR0_EL1或TTBR1_EL1定义ASID。0:TTBR0_EL1.ASID定义了ASID;1:TTBR1_EL1.ASID定义了ASID |

| 21:16 | T1SZ | TTBR1_EL1寻址的内存区域大小偏移量。区域大小为2的(64-T1SZ)次方字节。T1SZ的最大值和最小值取决于翻译表的级别和内存翻译粒度大小。 |

| 15:14 | TG0 | TTBR0_EL1的颗粒大小。01:16KB;10:4KB;11:64Kb |

| 13:12] | SH0 | 与使用TTBR0_EL1的翻译表有关的内存的可共享性属性。00:不共享;10:外部可共享;11:内部可共享 |

| 11:10 | ORGN0 | 与使用TTBR0_EL1的翻译表有关的内存的外部缓存属性。00:不缓存;01:写回的读写缓存;10:写穿的读缓存写不缓存;11:写回的读缓存写不缓存 |

| 9:8 | IRGN0 | 与使用TTBR0_EL1的翻译表有关的内存的内部缓存属性。00:不缓存;01:写回的读写缓存;10:写穿的读缓存写不缓存;11:写回的读缓存写不缓存 |

| 7 | EPD0 | 控制是否在TLB miss上对使用TTBR0_EL1进行转换的地址执行转换表遍历。0:使用TTBR0_EL1执行翻译表遍历;1:不执行翻译表遍历 |

| 6 | RES0 | 保留的 |

| 5:0 | T0SZ | TTBR0_EL1寻址的内存区域大小偏移量。区域大小为2的(64-T0SZ)次方字节。T0SZ的最大值和最小值取决于翻译表的级别和内存翻译粒度大小。 |

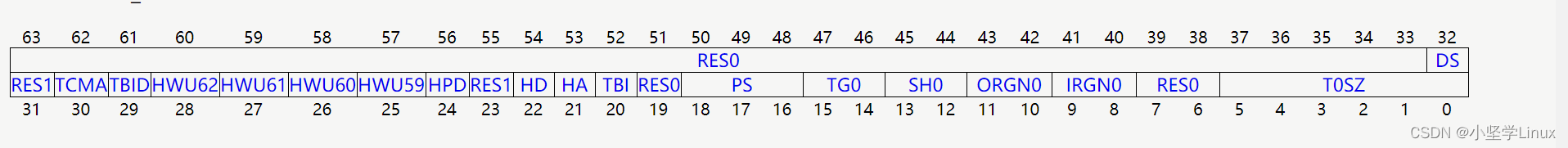

TCR_EL2&3:

| 位数 | 名称 | 含义 |

|---|---|---|

| 63:33 | RES0 | 保留的 |

| 32 | DS | 当在翻译制度的第1阶段使用4KB和16KB翻译粒时,该字段影响52位输出寻址,包括翻译描述符、块描述符、页描述符的输出情况 |

| 31 | RES1 | 保留的 |

| 30 | TCMA | 控制未检查访问的生成。 0:对EL2上未检查访问是不会影响其他。1:在EL2的所有访问都是未检查的。 |

| 29 | TBID | 使用指令地址的顶部字节进行地址匹配控制 。0:TCR_EL2.TBI0适用于指令访问和数据访问;1:TCR_EL2.TBI0仅适用于数据访问。 |

| 28 | HWU62 | 进行翻译的阶段1的时候,翻译表块或页条目的位[62]能否实现定义的硬件使用。0:不能;1:可以 |

| 27 | HWU61 | 进行翻译的阶段1的时候,翻译表块或页条目的位[61]能否实现定义的硬件使用。0:不能;1:可以 |

| 26 | HWU60 | 进行翻译的阶段1的时候,翻译表块或页条目的位[60]能否实现定义的硬件使用。0:不能;1:可以 |

| 25 | HWU59 | 进行翻译的阶段1的时候,翻译表块或页条目的位[59]能否实现定义的硬件使用。0:不能;1:可以 |

| 24 | HPD | 分级权限禁用,影响TTBR0 EL2指向的翻译表中的一些控制位。0:启用分级权限;1:禁用分级权限 |

| 23 | RES1 | 保留的 |

| 22 | HD | 从EL2转换阶段1脏态的硬件管理。 0:禁用脏状态的阶段1硬件管理;1:启用脏状态的阶段1硬件管理 |

| 21 | HA | 从EL2翻译的阶段1硬件访问标志更新。 0:阶段1访问标志位更新被禁用;1:阶段1访问标志位更新启用。 |

| 20 | TBI | 最高字节忽略。 0:地址计算中使用的Top字节匹配TTBR0_EL2区域的地址;1:地址计算中忽略的Top字节 |

| 19 | RES1 | 保留的 |

| 18:16 | PS | 物理地址大小。000:32位,4GB;001:36位,64GB;010:40位,1TB;011:42位,4TB;100:44位,16TB;101:48位,256TB;110:52位,4PB |

| 15:14 | TG0 | TTBR0_EL2的颗粒大小。01:16KB;10:4KB;11:64Kb |

| 13:12 | SH0 | 与使用TTBR0_EL2的翻译表有关的内存的可共享性属性。00:不共享;10:外部可共享;11:内部可共享 |

| 11:10 | ORGN0 | 与使用TTBR0_EL2的翻译表有关的内存的外部缓存属性。00:不缓存;01:写回的读写缓存;10:写穿的读缓存写不缓存;11:写回的读缓存写不缓存 |

| 9:8 | IRGN0 | 与使用TTBR0_EL2的翻译表有关的内存的内部缓存属性。00:不缓存;01:写回的读写缓存;10:写穿的读缓存写不缓存;11:写回的读缓存写不缓存 |

| 7:6 | RES0 | 保留的 |

| 5:0 | T0SZ | TTBR0_EL2寻址的内存区域大小偏移量。区域大小为2的(64-T0SZ)次方字节。T0SZ的最大值和最小值取决于翻译表的级别和内存翻译粒度大小。 |

4.系统控制寄存器(SCTLR_ELx)

系统控制寄存器(SCTLR)是一个用来控制标准内存、配置系统能力、提供处理器核状态信息的寄存器,包括 SCTLR_EL1、 SCTLR_EL2和 SCTLR_EL3。但是并不是所有bit在EL1都可用得。

| bit | 含义 |

|---|---|

| UCI | 设置此位后,在AArch64中为DC CVAU、DC CIVAC、DC CVAC和IC IVAU指令启用EL0访问。 |

| EE | 异常字节顺序。0表示小端,1表示大端。 |

| EOE | EL0显式数据访问的字节序。0表示小端,1表示大端。 |

| WXN | 写权限不可执行 XN (eXecute Never)。 0表示可写区域不设置不可执行权限(XN),1表示可写区域强制为不可执行(XN) |

| nTWE | 不陷入WFE,此标志为1表示WFE作为普通指令执行 |

| nTWI | 不陷入WFI, 此标志为1表示WFI作为普通指令执行 |

| UCT | 此标志为1时,开启AArch64的EL0下访问CTR_EL0寄存器 |

| DNE | EL0 下访问 DC AVA指令,0 禁止执行,1 允许执行 |

| I | 开启指令缓存,这是在EL0和EL1下的指令缓存的启用位。对可缓存的正常内存的指令访问被缓存。 |

| UMA | 用户屏蔽访问。当EL0使用AArch64,控制从EL0的中断屏蔽访问。 |

| SED | 禁止SETEND。在EL0使用AArch32禁止SETEND指令。0 使能,1 禁止 |

| ITD | 禁止IT指令。0表示IT指令有效,1表示IT指令被当作16位指令。仅另外16位指令或32位指令的头16位可以使用 |

| CP | 15BEN CP15 barrier使能。如果实现了,它是AArch32 CP15 DMB,DSB和ISB barrier操作的使能位 |

| SA0 | EL0的栈对齐检查使能位 |

| SA | 栈对齐检查使能位 |

| C | 数据cache使能。EL0和EL1的数据访问使能位。对cacheable普通内存的数据访问都被缓存 |

| A | 对齐检查使能位 |

| M | 使能MMU |

若想查看更加具体含义可以查看贺贺的个人网站。

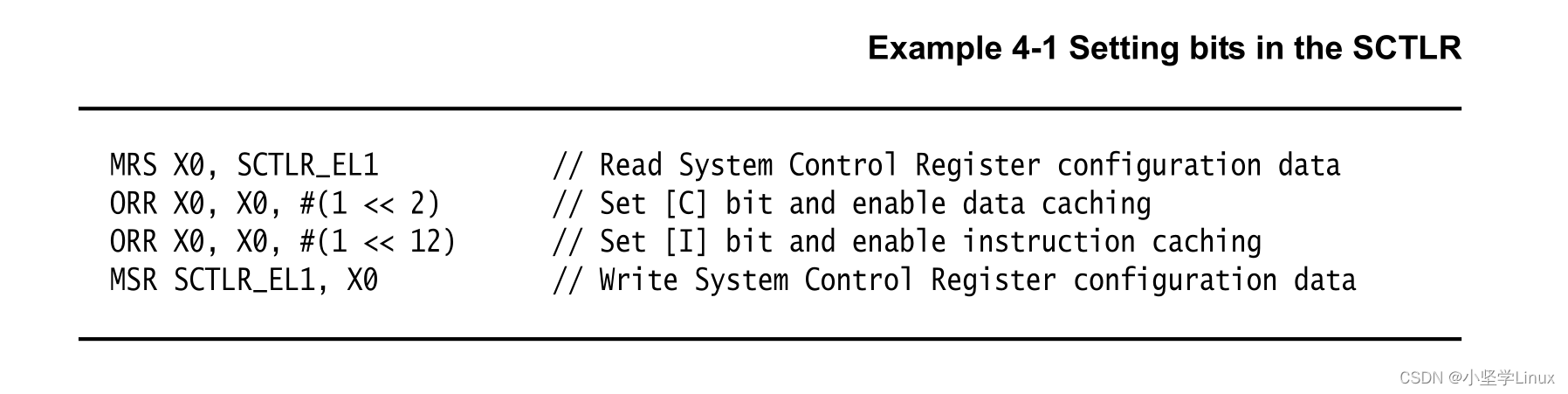

SCTLR_ELn的使用方式:

MRS <Xt>, SCTLR_ELn // Read SCTLR_ELn into Xt

MSR SCTLR_ELn, <Xt> // Write Xt to SCTLR_ELn

下图是cpu初始化的时候,操作SCTLR_EL1,打开指令cache和数据cache的例子:

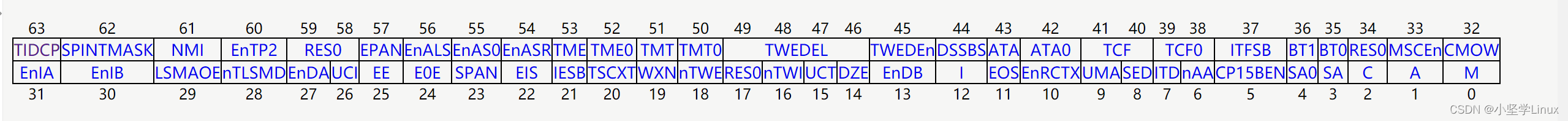

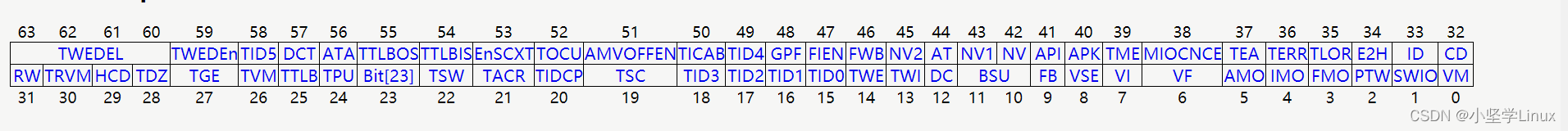

5. 虚拟化配置寄存器(HCR_EL2)

虚拟化配置寄存器(HCR_EL2)是一个用来为虚拟化提供配置控制的寄存器,包括定义各种操作是否被捕获到EL2。

| 位数 | 名称 | 含义 |

|---|---|---|

| 63:60 | TWEDEL | TWE延迟。当HCR_EL2.TWEDEn为1,由HCR_EL2引起的WFE*陷阱的最小延迟为2的(TWEDEL + 8)次方,单位周期。 |

| 59 | TWEDEn | TWE推迟启用。让由HCR EL2.TWE引起的WFE*指令延迟陷入可配置。 0:陷入的延迟是已经定义的;1:陷入的延迟至少是SCR_EL3.TWEDEL中定义的周期数。 |

| 58 | TID5 | 陷入ID组5.。0:任何指令不会被捕获;1:在EL1和EL0访问ID组寄存器5会被捕获到EL2 |

| 57 | DCT | 默认的可缓存性标记。当HCR_EL2.DC实际上控制的是阶段1翻译被视为标记还是或未标记的。0:未标记的;1:标记的 |

| 56 | ATA | 分配标签访问,控制在EL1和EL0对分配标签的访问。0:避免对分配标签的访问,访问GCR_EL1, RGSR_EL1, TFSR_EL1, TFSR_EL2 或者TFSRE0_EL1会出现未定义指令异常并且陷入EL2;1:允许对分配标签的访问 |

| 55 | TTLBOS | 操作于外层共享域的TLB维护陷入指令。当EL2在当前的Security状态中启用时,在EL1执行TLB*指令会导致,0:任何指令不会被捕获。1:指定指令的执行被陷入在EL2中。 |

| 54 | TTLBIS | 操作于内部共享域的TLB维护陷入指令。当EL2在当前的Security状态中启用时,在EL1执行TLB*指令会导致,0:任何指令不会被捕获。1:指定指令的执行被陷入在EL2中。 |

| 53 | EnSCXT | 启用对SCXTNUM_EL1和SCXTNUM_EL0寄存器的访问。0:当HCR_EL2.E2H为0或者HCR_EL2.TGE为0,则访问寄存器会导致未定义指令异常并且陷入EL2;1:访问寄存器不会导致陷入EL2 |

| 52 | TOCU | 操作到统一点的缓存维护陷入指令。当EL2在当前安全状态下启用时,将这些缓存维护指令的执行捕捉到EL2。0:任何指令不会被捕获;1:指定指令的执行会被困在EL2 |

| 51 | AMVOFFEN | 活动监视器虚拟偏移使能。0:活动监视器的虚拟化被禁用。间接读取虚拟偏移寄存器是零;1:启用了活动监视器的虚拟化 |

| 50 | TICAB | ICIALLUIS/IC IALLUIS缓存维护陷入指令。当EL2在当前安全状态下启用时,在EL1到EL2处捕捉那些缓存维护指令的执行。0:任何指令不会被捕获。1:指定指令的执行被陷入在EL2中。 |

| 49 | TID4 | 陷入ID组4。 0:任何指令不会被捕获;1:在EL1和EL0访问ID组寄存器4会被捕获到EL2 |

| 48 | GPF | 控制颗粒保护故障在EL0、EL1的上报。0:异常从EL0、EL1不会路由到EL2;1:异常从EL0、EL1路由到EL2,并报告为颗粒保护检查异常。 |

| 47 | FIEN | 故障注入启用。在EL1访问寄存器ERXPFGCDN_EL1, ERXPFGCTL_EL1和ERXPFGF_EL1的结果。0:从EL1访问指定的寄存器会产生一个到EL2的Trap异常;1:任何指令不会被被捕获 |

| 46 | FWB | 强迫写回。定义在2阶段转换机制的组合缓存属性。 |

| 45 | NV2 | 嵌套的虚拟化。改变HCR_EL2的行为。(NV1, NV)为硬件提供一种能够将系统寄存器的读写转换为内存的读写的机制。0:该位对HCR EL2的行为没有影响;1:如果HCR_EL2{NV1, NV} 开启了,则将寄存器的读/写转换为对内存的读/写和将EL2寄存器重定向到EL1寄存器。 |

| 44 | AT | 地址转换。当EL2在当前安全状态下启用时,在EL1执行AT S1E0R, AT S1E0W, AT S1E1R, AT S1E1W, AT S1E1RP, AT S1E1WP地址转换指令是否会被捕获到EL2。0:不会;1:会 |

| 43 | NV1 | 嵌套的虚拟化。0:没有作用;1:如果HCR_EL2.NV2为1 ,从EL1到实现的EL2寄存器的访问被转换为load和store;如果HCR_EL2.NV2为0,EL1访问VBAR_EL1, ELR_EL1, SPSR_EL1会陷入EL2 |

| 42 | NV | 嵌套的虚拟化。0:没有作用;1:如果HCR_EL2.NV2为0 ,EL1对指定寄存器的访问或指定指令的执行被捕获到EL2,如果HCR_EL2.NV2为1,重新定义EL1的寄存器,使用SPSR_EL2, ELR_EL2, ESR_EL2,和FAR_EL2代替SPSR_EL1, ELR_EL1, ESR_EL1和FAR_EL1 |

| 41 | API | 控制与指针身份验证相关的下列指令的使用。0:任何与指针验证相关的指令的使用都会被捕获到EL2;1:指令不会被捕获。 |

| 40 | APK | 当APK被设置为0,当EL2在当前安全状态下启用时,对保存指针身份验证“键”值的寄存器的访问被捕获到EL2。 |

| 39 | TME | 允许在EL0、EL1上访问TSTART、TCOMMIT、TTEST和TCANCEL指令。 0:不允许,定义为未定义指令;1:允许 |

| 38 | MIOCNCE | 使能用于EL1和EL0的翻译机制的不匹配的内部/外部缓存的非一致性。对于EL1&0翻译机制,对于使用共享性和缓存性的通用定义的内存位置的允许访问,如果这些访问的内部缓存属性与外部缓存属性不同,0:那么一定不会失去一致性;1:可能会失去一致性 |

| 37 | TEA | 路由同步外部中止异常到EL2。0:异常不会从EL0和EL1路由到EL2;1:当前Security状态下启用时,如果EL0和EL1的同步外部中止异常没有路由到EL3,则路由到EL2。 |

| 36 | TERR | 陷入错误记录访问。从EL1陷入到EL2读取的RAS错误寄存器。 0:任何指令不会被捕获。1:当EL2在当前安全状态下被启用时,访问EL1指定的寄存器会生成一个到EL2的陷入异常。 |

| 35 | TLOR | 陷入LOR寄存器。非安全的EL1访问LORSA_EL1, LOREA_EL1, LORN_EL1, LORC_EL1, 和 LORID_EL1。 0:不产生异常;1:被捕获到EL2 |

| 34 | E2H | EL2主机。启用主机操作系统在EL2中运行。0:在EL2上支持主机操作系统的设施被禁用。1:在EL2上支持主机操作系统的设施被启用。 |

| 33 | ID | 禁用阶段2指令访问缓存。0:这种控制对EL1和EL0翻译体系的第二阶段没有影响;1:强制所有对普通内存的指令访问的第二阶段转换为不可缓存。 |

| 32 | CD | 禁用阶段2数据访问缓存。0:这种控制对EL1和EL0翻译体系的第二阶段没有影响;1:强制所有对普通内存的指令访问的第二阶段转换为不可缓存。 |

| 31 | RW | 对较低异常级别的执行状态控制。0:低层的特权等级全部都是AArch32;1:低一层的特权等级是 AArch64 |

| 30 | TRVM | 陷入读取虚拟内存控制。从EL陷入到EL21读取虚拟内存控制寄存器。0:任何指令不会被捕获。1:当EL2在当前安全状态下启用时,对指定虚拟内存控件的EL1读访问被捕获到EL2。 |

| 29 | HCD | HVC指令禁用。0:在EL2和EL1上启用HVC指令执行;1:HVC指令在EL2和EL1是未定义的,任何产生的异常都被带到执行HVC指令的异常级别。 |

| 28 | TDZ | DC ZVA指令陷入。当EL2在当前Security状态下启用时,在EL0和EL1执行DC ZVA指令将陷入EL2。0:不会陷入;1:当EL2在当前Security中启用时,任何试图执行该指令会被捕获到EL2。 |

| 27 | TGE | 陷入一般异常。0:对ELO的执行没有影响;1:当EL2在当前安全状态下未启用时,对EL0没有影响。当EL2在当前安全状态下启用时,所有异常路由到EL2 |

| 26 | TVM | 虚拟内存控制陷入。0:任何指令不会被捕获;1:当EL2在当前安全状态下启用时,对指定的EL1虚拟内存控制寄存器的EL1写访问被捕获到EL2。 |

| 25 | TTLB | TLB维护指令陷入。0:任何指令不会被捕获;1:当EL2在当前安全状态下启用时,在EL1执行指定的TLB维护指令会被捕获到EL2。 |

| 24 | TPU | 缓存维护指令陷入,操作到统一点。0:任何指令不会被捕获;1:当EL2在当前安全状态下启用时,在EL1执行指定的缓存维护指令会被捕获到EL2。 |

| 23 | TPCP | 数据或统一的缓存维护指令陷入,操作到一致性或持久性点。0:任何指令不会被捕获;1:当EL2在当前安全状态下启用时,在EL1执行指定的缓存维护指令会被捕获到EL2。 |

| 22 | TSW | 数据或通过“设置/方式”操作的统一缓存维护指令陷入。0:任何指令不会被捕获;1:当EL2在当前安全状态下启用时,在EL1执行指定的缓存维护指令会被捕获到EL2。 |

| 21 | TACR | 辅助控制寄存器陷入。0:任何指令不会被捕获;1:当EL2在当前安全状态下启用时,在EL1访问辅助控制寄存器会被捕获到EL2。 |

| 20 | TIDCP | 实现定义的功能陷入。。0:任何指令不会被捕获;1:当EL2在当前Security状态中启用时,EL1访问或执行保留的指定编码实现定义功能被捕获到EL2。 |

| 19 | TSC | smc指令陷入。0:任何指令不会被捕获;1:当EL2在当前安全状态下启用时,在EL1执行smc指令会被捕获到EL2。 |

| 18 | TID3 | 陷入ID组3。 0:任何指令不会被捕获;1:在EL1和EL0访问ID组寄存器3会被捕获到EL2 |

| 17 | TID2 | 陷入ID组2。 0:任何指令不会被捕获;1:在EL1和EL0访问ID组寄存器2会被捕获到EL2 |

| 16 | TID1 | 陷入ID组1。 0:任何指令不会被捕获;1:在EL1和EL0访问ID组寄存器1会被捕获到EL2 |

| 15 | TID2 | 陷入ID组0。 0:任何指令不会被捕获;1:在EL1和EL0访问ID组寄存器0会被捕获到EL2 |

| 14 | TWE | 当被设置为1,在任何低于EL2的异常级别上执行WFE指令的任何尝试都会被捕获到EL2 |

| 13 | TWI | 当被设置为1,在任何低于EL2的异常级别上执行WFI指令的任何尝试都会被捕获到EL2 |

| 12 | DC | 默认的缓存能力。 0:对EL1和EL0翻译策略没有影响;1:EL1和El0翻译阶段1产生的记忆类型为非正常可共享的,内部写回式读分配写分配,外部写回式读分配写分配。 |

| 11:10 | BSU | 屏障共享升级。该字段确定从EL1或EL0执行的指令屏障的最小可共享域。00:不共享;01:内核共享;10:外部共享;11:全部共享 |

| 9 | FB | 强制广播。 0:任何指令不会被捕获;1:在EL1执行指定的指令之一时,该指令会在内部共享域中广播。 |

| 8 | VSE | 虚拟SError中断。 0:不会使一个虚拟的SError中断挂起;1:使一个虚拟的SError中断挂起 |

| 7 | VI | 虚拟IRQ中断。 0:不会使一个虚拟的IRQ中断挂起;1:使一个虚拟的IRQ中断挂起 |

| 6 | VF | 虚拟FIQ中断。 0:不会使一个虚拟的FIQ中断挂起;1:使一个虚拟的FIQ中断挂起 |

| 5 | AMO | 物理SError中断路由。当在EL2以下的Exception级别执行时,并且EL2在当前的Security状态下被启用,0:如果HCR_EL2.TGE为0,路由到EL2,如果HCR_EL2.TGE为1,不执行。1:路由到EL2,如果HCR_EL2.TGE为1,启用虚拟SError中断。 |

| 4 | IMO | 物理IRQ中断路由。当在EL2以下的Exception级别执行时,并且EL2在当前的Security状态下被启用,0:如果HCR_EL2.TGE为0,路由到EL2,如果HCR_EL2.TGE为1,不执行。1:路由到EL2,如果HCR_EL2.TGE为1,启用虚拟IRQ中断。 |

| 3 | FMO | 物理FIQ中断路由。当在EL2以下的Exception级别执行时,并且EL2在当前的Security状态下被启用,0:如果HCR_EL2.TGE为0,路由到EL2,如果HCR_EL2.TGE为1,不执行。1:路由到EL2,如果HCR_EL2.TGE为1,启用虚拟FIQ中断。 |

| 2 | PTW | 受保护的表遍历。在EL1&EL0转换体系中,作为第一阶段转换表遍历的一部分的转换表访问要服从第二阶段转换。来自两个转换阶段的内存类型属性的组合意味着可以访问某种类型的Device内存。0:转换表的遍历发生在普通非缓存内存中。这意味着它可以被推测;1:内存访问产生二级权限故障 |

| 1 | SWIO | 设置/失效指令覆盖。0:通过设置/失效指令对数据缓存无效的操作没有影响;1:通过设置/失效指令使数据失效,达到清理数据缓存的目的 |

| 0 | VM | 虚拟化支持。当EL2在当前安全状态下启用时,为el1和o转换机制启用阶段2地址转换。0:禁用;1:启用 |

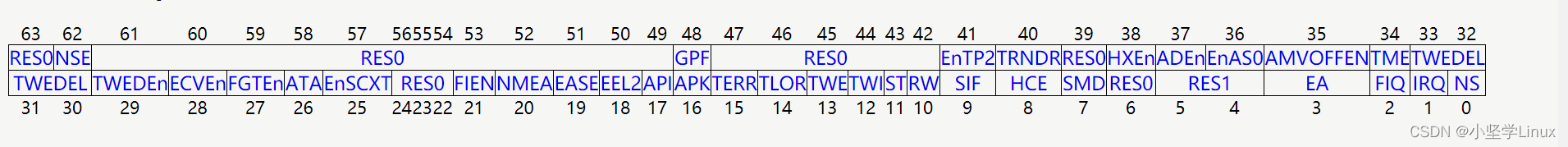

6.安全配置寄存器(SCR_EL3)

安全配置寄存器(SCR_EL3)是一个定义当前Security状态的配置的寄存器,它指定:EL0、EL1、EL2的安全状态。“安全”状态为“安全”或者“不安全”。

| 位数 | 名称 | 含义 |

|---|---|---|

| 63 | RES0 | 保留的 |

| 62 | NSE | 该字段表示根据SCR_EL3.NS,选择EL2及以下Exception级别的Security状态。 |

| 61:49 | RES0 | 保留的 |

| 48 | GPF | 控制颗粒保护故障在EL0、EL1和El2的上报。0:异常从EL0、EL1或EL2不会路由到EL3;1:异常从EL0、EL1或EL2路由到EL3,并报告为颗粒保护检查异常。 |

| 47:42 | RES0 | 保留的 |

| 41 | EnTP2 | 在EL2、EL1和EL0上执行的trap指令(比如访问TPIDR2_EL0)陷入到EL3。0:这些指令会在EL2、EL1和EL0的执行时被捕获;1:任何指令的执行不会被捕获。 |

| 40 | TRNDR | RNDR和RNDRRS读取是否捕获。0:不会导致RNDR和RDNRRS被捕获。;1:任何读取RNDR或RNDRRS的尝试都被陷入到EL3 |

| 39 | RES0 | 保留的 |

| 38 | HXEn | 允许从EL3访问EL2上的HCRX_EL2寄存器。0:不允许,间接读会返回0;1:允许 |

| 37 | ADEn | 允许EL1和EL2上访问ACCDATA_EL1寄存器。0:在 EL1 at EL1和EL2访问ACCDATA_EL1会被捕获到EL3,除非访问被EL2细粒度trap捕获到EL2;1:访问ACCDATA_EL1不会被捕获。 |

| 36 | EnAS0 | 在EL0, EL1或EL2触发ST64BVO指令异常是否路由到EL3。0:路由EL3;1:不会路由到EL3 |

| 35 | AMVOFFEN | 活动监视器虚拟偏移使能。0:使能,在EL2访问AMEVCNTVOFF0_EL2和AMEVCNTVOFF1_EL2 寄存器会陷入到EL3;1:不使能 |

| 34 | TME | 允许在EL0、EL1和EL2上访问TSTART、TCOMMIT、TTEST和TCANCEL指令。 0:不允许,定义为未定义指令;1:允许 |

| 33:30 | TWEDEL | TWE延迟。当SCR_EL3.TWEDEn为1,由SCR_EL3引起的WFE*陷阱的最小延迟为2的(TWEDEL + 8)次方,单位周期。 |

| 29 | TWEDEn | TWE推迟启用。让由SCR EL3.TWE引起的WFE*指令延迟陷入可配置。 0:陷入的延迟是已经定义的;1:陷入的延迟至少是SCR_EL3.TWEDEL中定义的周期数。 |

| 28 | ECVEn | ECV启用,启用对CNTPOFF_EL2寄存器的访问。0:EL2访问CNTPOFF_EL2会被捕获到EL3,;1:EL2访问CNTPOFF_EL2不陷入在EL3。 |

| 27 | FGTEn | 细粒度的陷阱使能。控制对HAFGRTR_EL2, HDFGRTR_EL2, HDFGWTR_EL2, HFGRTR_EL2, HFGITR_EL2,和HFGWTR_EL2,寄存器的访问。 0:会陷入EL3;1:不会陷入EL3 |

| 26 | ATA | 分配标签访问,控制在EL2, EL1和EL0对分配标签的访问。0:避免对分配标签的访问,访问GCR_EL1, RGSR_EL1, TFSR_EL1, TFSR_EL2 或者TFSRE0_EL1会出现未定义指令异常并且陷入EL3;1:允许对分配标签的访问 |

| 25 | EnSCXT | 使能对SCXTNUM_EL2、SCXTNUM_EL1和SCXTNUM_ELO 寄存器的访问。0:不使能,访问读取返回0并且会陷入EL3;1:使能 |

| 24:22 | RES0 | 保留的 |

| 21 | FIEN | 故障注入启用。在EL1和EL2访问寄存器ERXPFGCDN_EL1, ERXPFGCTL_EL1和ERXPFGF_EL1的结果。0:从EL1和EL2访问指定的寄存器会产生一个到EL3的Trap异常;1:任何指令不会被被捕获 |

| 20 | NMEA | 屏敝外部中止。当SCR_EL3.EA 等于1时,0:SError中断不会路由到EL3;1:由PSTATE.A.决定是否把SError中断路由到EL3 |

| 19 | EASE | 外部中断到SError中断向量。同步执行到EL3的外部终止异常会被执行到的位置,0:VBAR_EL3相对应的同步异常向量;1:VBAR_EL3相对应的SError中断向量。 |

| 18 | EEL2 | 安全EL2启用。 0:与Secure EL2相关的行为都被禁用;1:与Secure EL2相关的行为都已启用。 |

| 17 | API | 控制与指针身份验证相关的下列指令的使用。0:任何与指针验证相关的指令的使用都会被捕获到EL3;1:指令不会被捕获。 |

| 16 | APK | 当APK被设置为1,对持有EL1或EL2指针认证“键”值的寄存器的访问被捕获到EL3,除非它们由于HCR_EL2.APK位或其他陷阱而被捕获到EL2。 |

| 15 | TERR | Trap错误记录访问。0:不产生异常;1:从EL1和EL2访问指定的寄存器会产生一个到EL3的Trap异常。 |

| 14 | TLOR | 0:不产生异常;1:如果EL1和EL2访问的LOR寄存器不是未定义的,则被捕获到EL3,除非它被捕获到HCR_EL2 |

| 13 | TWE | 当被设置为1,在任何低于EL3的异常级别上执行WFE指令的任何尝试都会被捕获到EL3 |

| 12 | TWI | 当被设置为1,在任何低于EL3的异常级别上执行WFI指令的任何尝试都会被捕获到EL3 |

| 11 | ST | 当被设置为1, Secure EL1访问counter timer物理安全计时器寄存器会被捕获到EL3 |

| 10 | RW | 对较低异常级别的执行状态控制。0:低层的特权等级全部都是AArch32;1:低一层的特权等级是 AArch64 |

| 9 | SIF | 安全指令取出。当PE处于Secure状态时,在翻译的第一阶段标记为Non-secure,该位决定是否允许从翻译的第一阶段标记为不安全的内存中提取安全状态指令。0:允许;1:不允许 |

| 8 | HCE | Hypervisor调用指令启用。0:HVC指令未定义的;1:在EL3、EL2、EL1使能HVC指令。 |

| 7 | SMD | 安全监控呼叫禁用。0:SMC指令在EL3、EL2和EL1使能;1:SMC指令未定义的。 |

| 6 | RES0 | 保留的 |

| 5:4 | RES1 | 保留的 |

| 3 | EA | 外部中止和错误中断路由。当在EL3以下的异常级别执行时,External aborts和SError中断会不会被路由到EL3。0:不会,但是在EL3时,SError中断不会被处理,外部中止中断会被处理;1:会 |

| 2 | FIQ | 物理FIQ路由。 当在EL3以下的异常级别执行时,物理FIQ中断会不会被路由到EL3。0:不会,但是在EL3执行时,不使用物理FIQ中断;1:会。 |

| 1 | IRQ | 物理IRQ路由。 当在EL3以下的异常级别执行时,物理IRQ中断会不会被路由到EL3。0:不会,但是在EL3执行时,不使用物理IRQ中断;1:会。 |

| 0 | NS | 不安全位。该字段与SCR_EL3.NSE选择EL2及更低异常水平的安全状态。 当NSE为0时,0:安全;1:不安全。 当NSE为1时,0:保留;1:领域 |

| 想要访问SCR_EL3,对该寄存器的读写只有在EL3下可以使用以下汇编指令: |

MRS <Xt>, SCR_EL3

MSR SCR_EL3, <Xt>

版权声明:本文内容由互联网用户自发贡献,该文观点与技术仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 dio@foxmail.com 举报,一经查实,本站将立刻删除。